5 Basic Instruction

5.12 MC, MCR

90

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

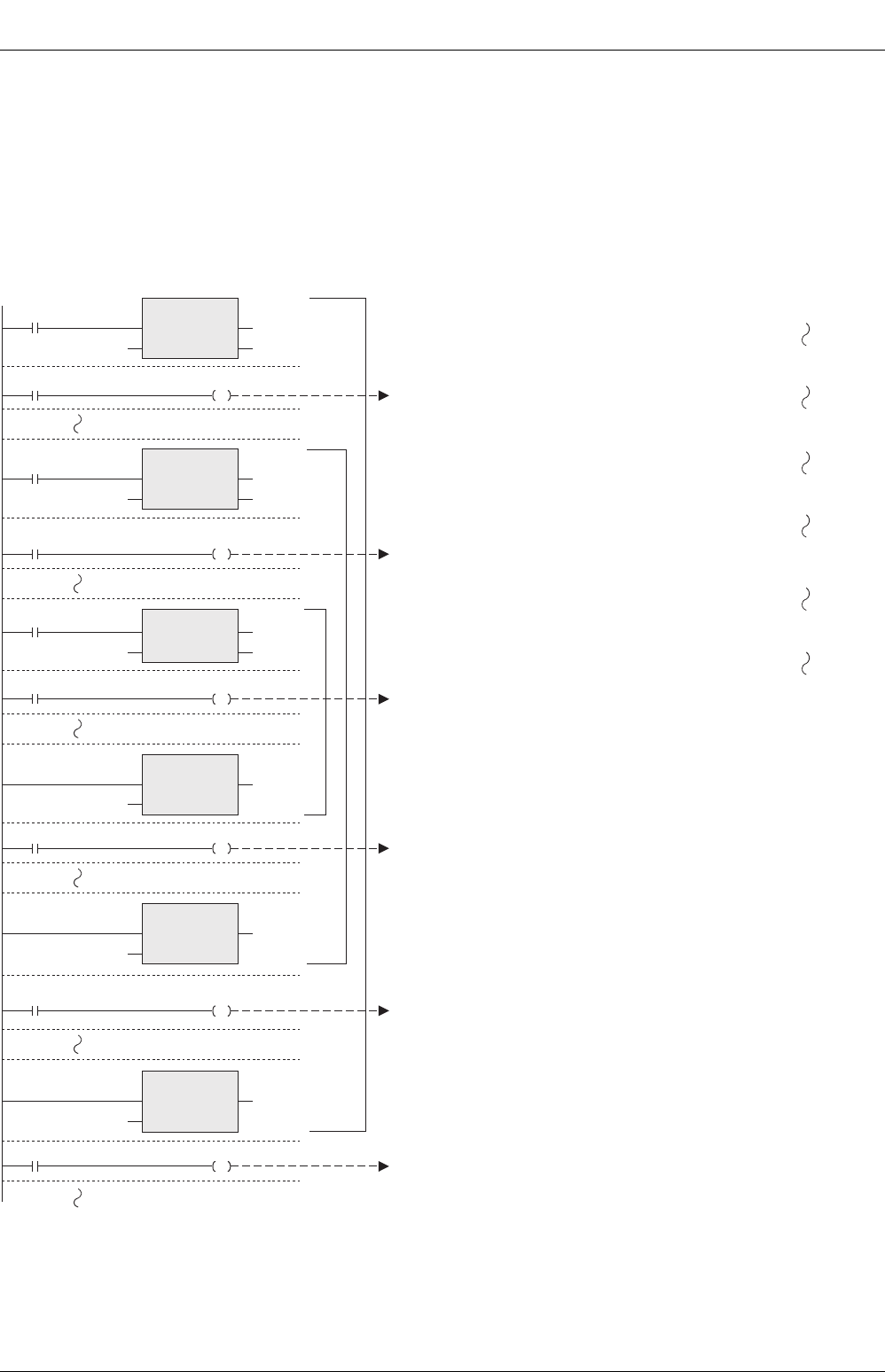

2. When the nesting structure is adopted.

When using MC instructions inside MC instruction, increase the nesting level "N" in turn in the way "N0 → N1

→ N2 → N3 → N4 → N5 → N6 → N7".

For returning from the nesting structure, reset the nesting levels from the highest one in turn using MCR

instruction in the way "N7 → N6 → N5 → N4 → N3 → N2 → N1 → N0".

For example, if "MCR N5" is programmed without programming "MCR N6" and "MCR N7", the nesting level is

returned to 5 at one time.

Available nesting levels are from N0 to N7 (eight layers).

X000

MC

EN

ENO

d

n

0 M100

N0

[Structured ladder/FBD]

Executes when X000 is ON.

X001

Y000

X002

MC

EN

ENO

d

n

1 M101

X003

Y001

X004

MC

EN

ENO

d

n

2 M102

X005

Y002

MCR

EN

ENO

n

2

X006

Y003

MCR

EN

ENO

n

1

X007

Y004

MCR

EN ENO

n

0

X010

Y005

N1

N2

N1

N0

N2

[ ST ]

MC(X000,0,M100);

Y000:= X001;

MC(X002,1,M101);

Y001:= X003;

MC(X004,2,M102);

Y002:= X005;

MCR(TRUE,2);

Y003:= X006;

MCR(TRUE,1);

Y004:= X007;

MCR(TRUE,0);

Y005:= X010;

Executes when X000 and X002 are ON.

Executes when X000, X002 and X004 are ON.

Not related to the status of X000, X002 and X004.

Executes when X000 and X002 are ON.

Executes when X000 is ON.