9 Applied Instructions (Arithmetic and Logical Operation)

9.4 DIVP / Division

180

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

Cautions

1) Some restrictions to applicable devices

S1:The FX

3G, FX3GC, FX3U and FX3UC PLCs only are applicable.

S2:The FX

3U and FX3UC PLCs only are applicable.

S3:Available only for a 16-bit operation. Not available for a 32-bit operation.

2) Instructions of pulse operation type are not provided in the FX

0S, FX0 or FX0N PLC.

To execute pulse operation, make the instruction execution condition pulse type.

3) The most significant bit of the quotient and remainder indicates the sign (positive: 0 or negative: 1).

4) The quotient is negative when either the dividend or divisor is negative.

The remainder is negative when the dividend is negative.

5) The remainder is not obtained when a bit device is specified with digit specification for the device

specified by .

6) In a 32-bit operation (by DDIV or DDIVP), Z cannot be specified as the device specified by .

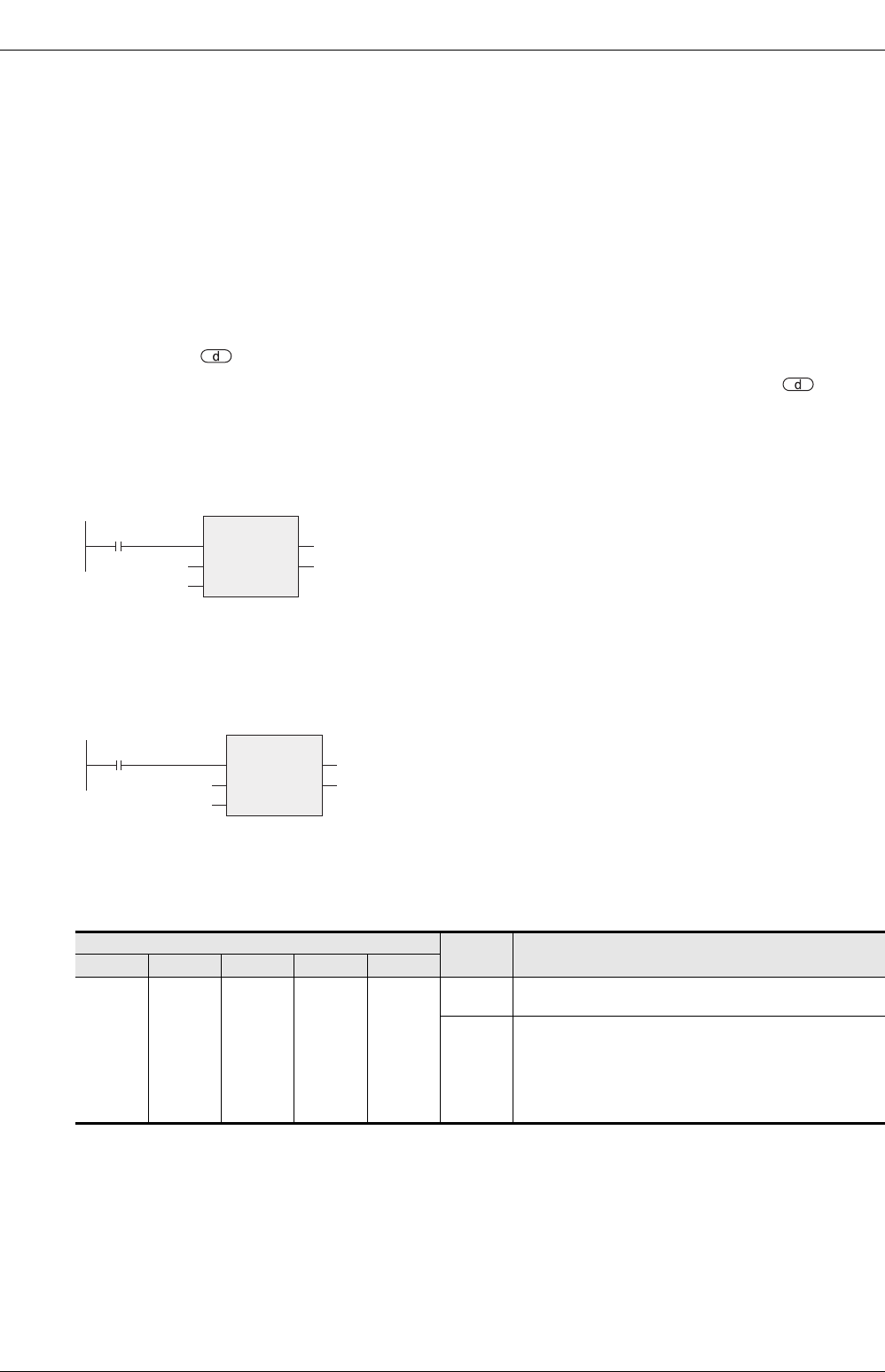

Program examples

1. 16-bit operation

2. 32-bit operation

Function changes according to versions

Compatible versions

Item Function summary

FX3S FX3G FX3GC FX3U FX3UC

Ver. 1.00

or later

Ver. 1.00

or later

Ver. 1.40

or later

Ver. 2.30

or later

Ver. 2.30

or later

Zero flag

Turns M8304 ON when the operation result of DIV instruction

is 0.

Carry flag

Turns M8306 ON when the operation result of DIV instruction

overflows.

16-bit operation : Only when the maximum negative value

(-32,768) is divided by "-1".

32-bit operation : Only when the maximum negative value

(-2,147,483,648) is divided by "-1".

(D 0) ÷ (D 2) → (D 4) ··· (D 5)

100 33 3 1

DIVP

EN

s1

s2

ENO

d

[Structured ladder/FBD]

[ ST ]

DIVP(X000,D0,D2,D4);

X000

D0

D2

Dividend Divisor Quotient Remainde

r

D4

(D 1, D 0) ÷ (D 3, D 2) → (D 5, D 4) ··· (D 7, D 6)

100,000 3,333 30 10

X001

D4D0

D2

[Structured ladder/FBD]

[ ST ]

DDIV(X001, D0, D2, D4);

DDIV

EN

s1

s2

ENO

d

Dividend Divisor Quotient Remainde

r