12 Applied Instructions (High Speed Processing)

276

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

12.5 DHSCR / High Speed Counter Reset

Function and operation explanation

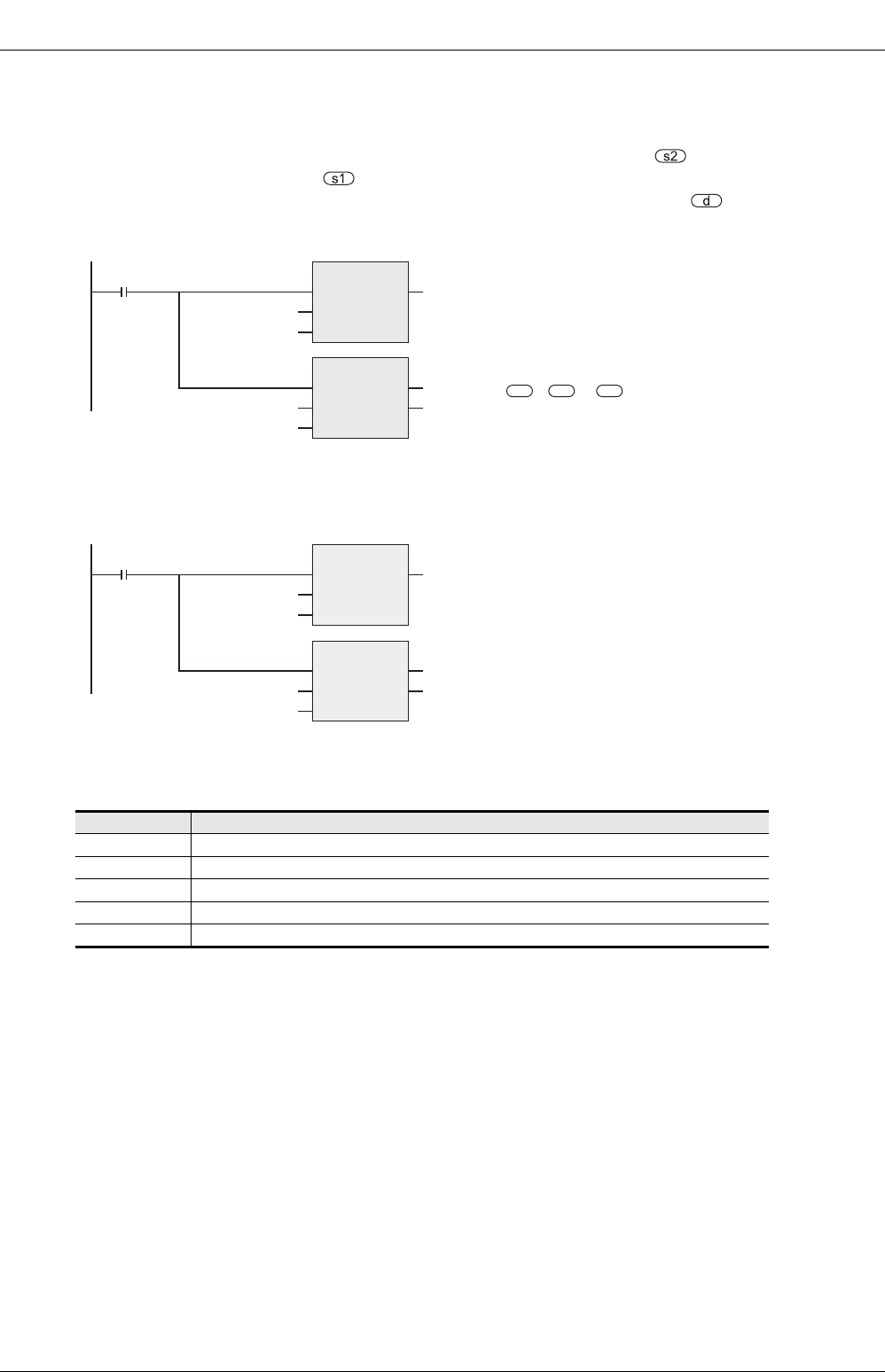

1. 32-bit operation (DHSCR)

When the current value of the high speed counter of the device specified by becomes the comparison

value of the device specified by (for example, when the current value changes from "199" to "200" or

from "201" to "200" if the comparison value is K200), the bit device specified by is reset (set to OFF)

regardless of the operation cycle. In this instruction, the comparison processing is executed after the counting

processing in the high speed counter.

Operation

When the current value of the high speed counter C255 changes (counts) from "99" to "100" or from "101" to

"100", Y010 is reset (output refresh).

Related instruction

The following instructions can be combined with high speed counters.

Instruction Instruction name

DHSCS High speed counter set

DHSCR High speed counter reset

DHSZ High speed counter zone compare

DHCMOV High speed counter move

DHSCT High speed counter compare with data table

Command input

Comparison value

Comparison source

DHSCR

EN

s1

s2

ENO

d

Output

destination

OUT_C_32

EN

CCoil

CValue

ENO

CC235

=

→

Reset

s1 s2 d

M8000

RUN

monitor

DHSCR

EN

s1

s2

ENO

d

K100

CN235

Y010 K100 = →CN235 Y010

OUT_C_32

EN

CCoil

CValue

ENO

CC235

K2147483647

Reset