12 Applied Instructions (High Speed Processing)

270

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

12.4 DHSCS, DHSCS_I / High Speed Counter Set, High Speed Interrupt Counter Set

4. Some restrictions to applicable devices

S1: The FX3U and FX3UC PLCs only are applicable.

Not indexed (V, Z).

S2: The FX

3G, FX3GC, FX3U and FX3UC PLCs only are applicable.

S3: The FX

3U and FX3UC PLCs only are applicable.

S4: When executing counter interrupt, the interrupt pointer is specified using the DHSCS_I instruction.

(Not available for the FX

0S, FX0, FX0N, FX1S, FX1N, FX1NC, FX3S, FX3G or FX3GC PLC.)

→ For the counter interrupt using this instruction, refer to Section 35.6.

5. Precedence of DHSCS, DHSCR and DHSZ instructions to one particular high speed counter

→ Refer to caution 6 in "Common cautions on using instructions for high speed counter" which is

described later.

6. Reset operation by an external terminal

→ Refer to caution 5 in "Common cautions on using instructions for high speed counter" which is

described later.

7. Other cautions on use

→ Refer to caution in "Common cautions on using instructions for high speed counter" which is

described later.

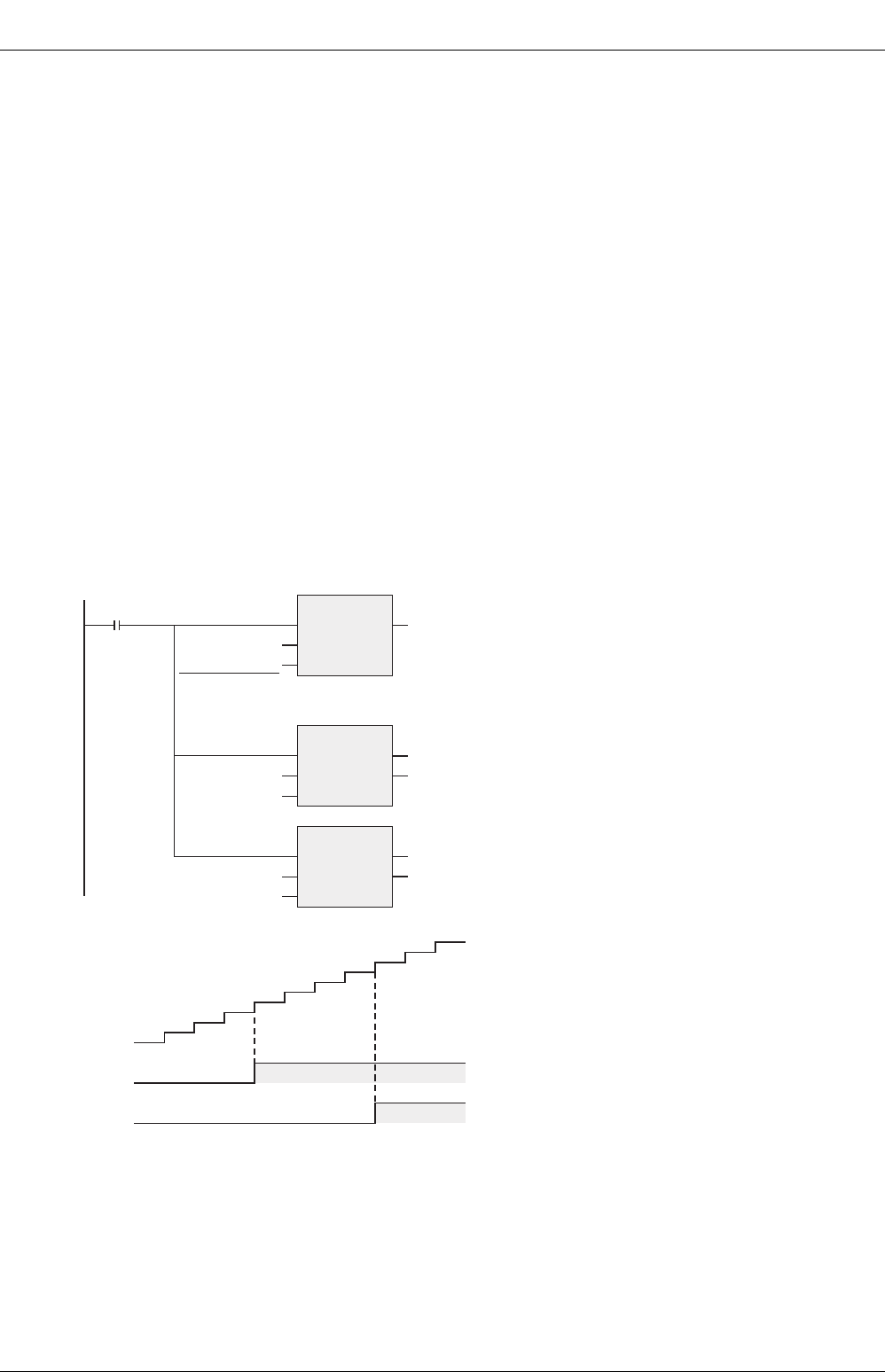

Program examples

With regard to the current value of a counter, different outputs (Y) are arbitrarily set to ON by two values.

C255

Y010

Y011

0

...

99

100

101

...

149

150

151

DHSCS

EN

s1

s2

ENO

d

M8000

RUN

monitor

Set the maximum counting value of high speed counter.

CN251=K100

→

Y010=ON

CN251=K150

→

Y011=ON

DHSCS

EN

s1

s2

ENO

d

CN251

CN251

Y010

Y011

K100

[Structured ladder/FBD]

OUT_C_32

EN

CCoil

CValue

ENO

CC251

K2147483647

K150

[ST]

OUT_C_32(M8000,CC251,K2147483647);

DHSCS(M8000,K100,CN251,Y010);

DHSCS(M8000,K150,CN251,Y011);