9 Applied Instructions (Arithmetic and Logical Operation)

9.10 NEG / Negation

192

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

9.10 NEG / Negation

Outline

This instruction obtains the 2's complement of a numeric value (by inverting each bit and adding "1").

A sign of a numeric value can be converted by this instruction.

→ For the floating point sign inversion instruction [DENEG], refer to Section 18.16.

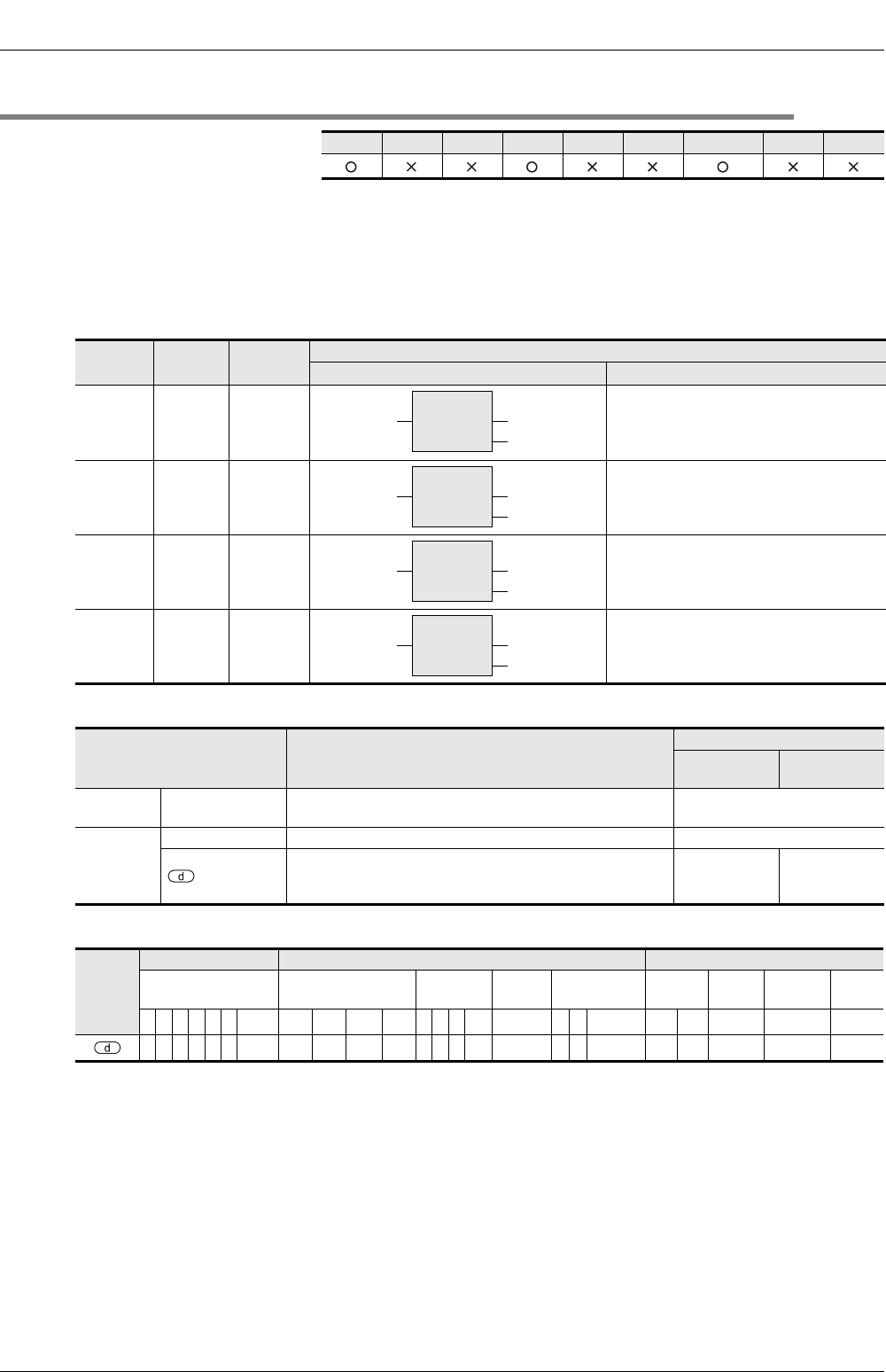

1. Format and operation, execution form

2. Set data

3. Applicable devices

S: Refer to "Cautions".

FX3U(C) FX3G(C) FX3S FX2N(C) FX1N(C) FX1S FXU/FX2C FX0N FX0(S)

Instruction

name

Operation

Execution

form

Expression in each language

Structured ladder/FBD ST

NEG 16 bits Continuous NEG(EN,d);

NEGP 16 bits Pulse NEGP(EN,d);

DNEG 32 bits Continuous DNEG(EN,d);

DNEGP 32 bits Pulse DNEGP(EN,d);

Variable Description

Data type

16-bit

operation

32-bit

operation

Input

variable

EN Execution condition Bit

Output

variable

ENO Execution state Bit

Word device which stores data for obtaining complement and will

store the operation result. (The operation result will be stored in

the same word device.)

ANY16 ANY32

Operand

type

Bit Devices Word Devices Others

System User Digit Specification

System

User

Special

Unit

Index

Constant

Real

Number

Character

String

Pointer

XYMTCS

D

.b

KnX KnY KnM KnS T C D R

U\G

VZModifier K H E

"

"

P

zzzzzz

S1 S1

zz z

NEG

EN ENO

d

NEGP

EN ENO

d

DNEG

EN ENO

d

DNEGP

EN ENO

d