10 Applied Instructions (Rotation and Shift Operation)

10.6 SFTL / Bit Shift Left

212

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

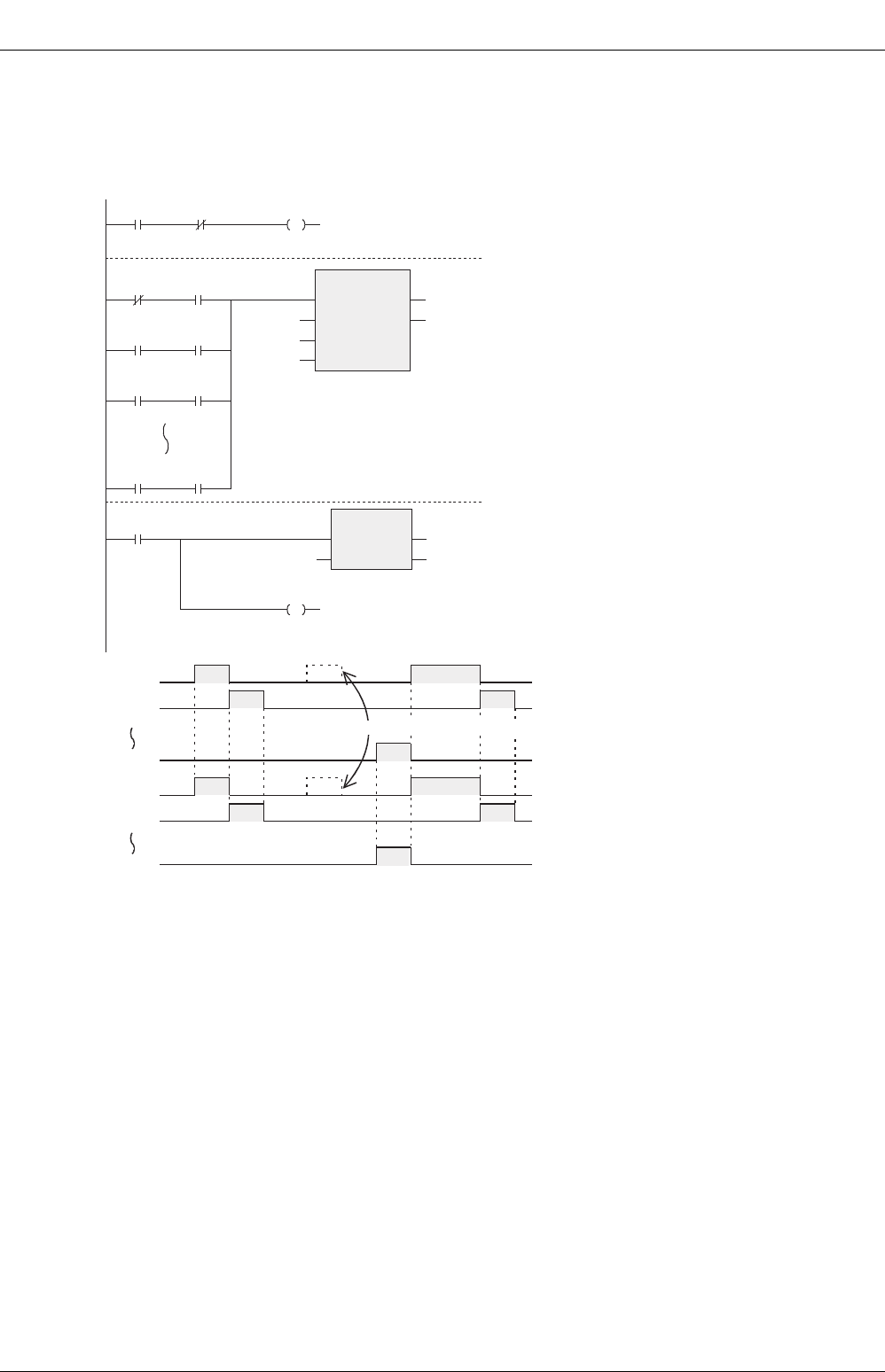

Program examples(Conditional stepping of 1-bit data)

By setting X000 to X007 to ON in turn, Y000 to Y007 are activated in turn.

If the order is wrong, activation is disabled.

X000

S 0

M8046

S 1

S 7

M8000

X000

M8046

X001

X002

X000

Head data

Data input

(S7 to S0) → (Y007 to Y000)

Bit 1 of M0 is regarded as the head input,

and 8-bit shift register is constructed by S0 to S7.

Even if X000 is set to ON, Y000 is not activated.

X000

X001

X007

Y001

Y007

Y000

*1

*1:By using a state relay (S), the state under operation

can be monitored by the dynamic monitoring function of

the state relay.

STL monitor is valid.

SFTL

EN

s

n1

ENO

d

n2

M0

S0

K8

K1

MOV

EN

s

ENO

d

K2S0

K2Y000

M0

M8047

[Structured ladder/FBD]

[ ST ]

M0:= X000 AND NOT M8046;

SFTL((NOT M8046 AND X000) OR (S0 AND X001) ··· OR (S1 AND X002) R(S7 AND X000), M0, K8, K1, S0);

MOV(M8000, K2S0, K2Y000);

M8047:= M8000;