24 Applied Instructions (Others)

24.4 CRC / Cyclic Redundancy Check

595

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

21

Applied Instructions

(Real Time

Clock Control)

22

Applied Instructions

(External Device)

23

Applied Instructions

(Extension

Function)

24

Applied Instructions

(Others)

25

Applied Instructions

(Block Data

Operation)

26

Applied Instructions

(Character

String Control)

27

Applied Instructions

(Data Operation 3)

28

Applied Instructions

(Data Comparison)

29

Applied Instructions

(Data Table

Operation)

30

Applied Instructions

(External Device

Communication)

Error

An operation error is caused in the following cases. The error flag M8067 turns ON, and the error code is

stored in D8067.

1) When any digits other than 4 digits are specified as the devices specified as or in digit

specification of bit device (error code: K6706)

2) When n is outside the allowable range (1 to 256) (error code: K6706)

3) When a device specified by +n-1 or +1 is outside the allowable range (error code: K6706)

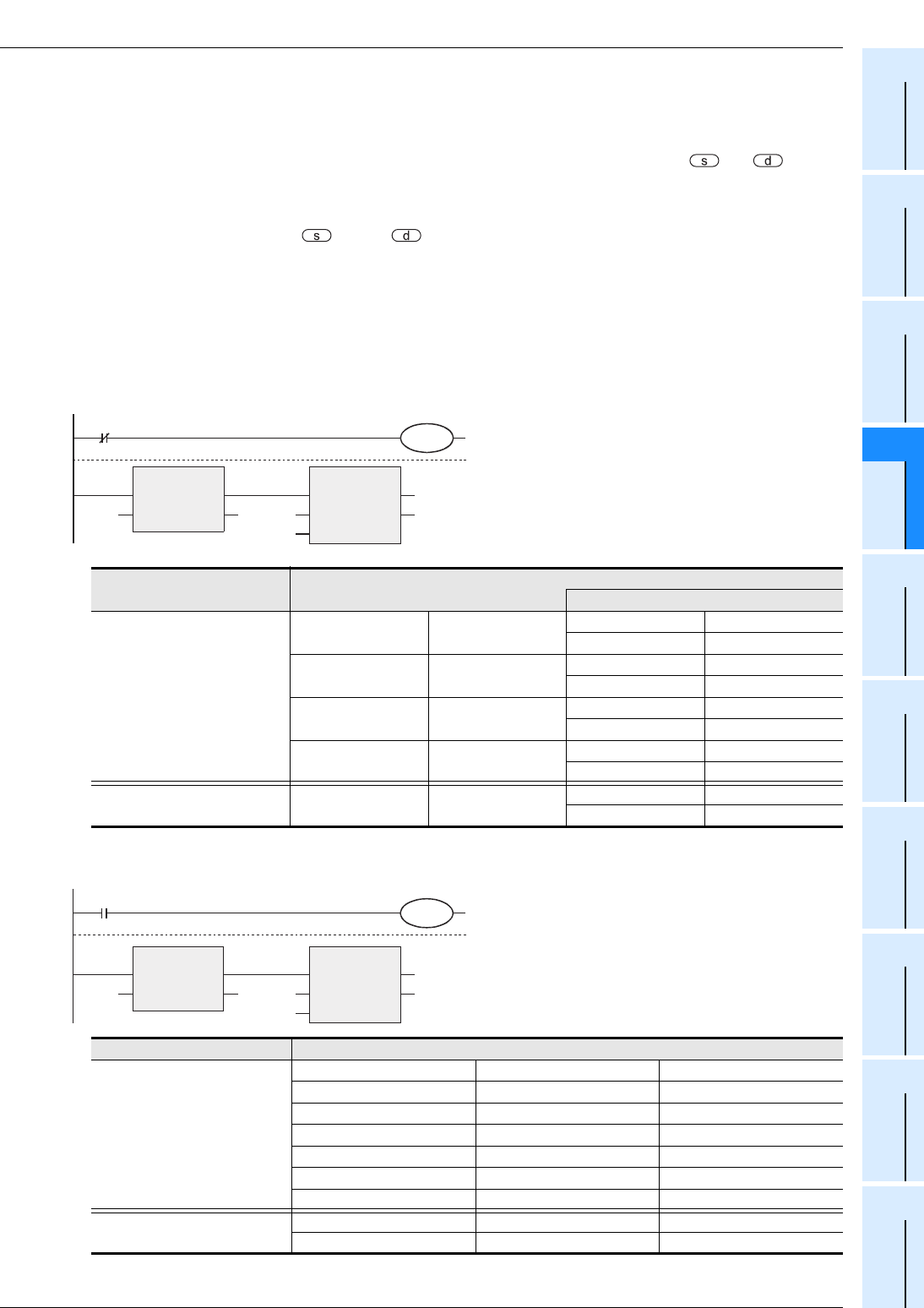

Program examples

In the program example shown below, the CRC value of the ASCII code "0123456" stored in D100 to D106 is

generated and stored to D0 when M0 turns ON.

1. In the case of 16-bit mode

2. In the case of 8-bit mode

Contents of data

Target data

Device storing data for which the

CRC value is generated

D100 3130H

Low-order byte 30H

High-order byte 31H

D101 3332H

Low-order byte 32H

High-order byte 33H

D102 3534H

Low-order byte 34H

High-order byte 35H

D103 3736H

Low-order byte 36H

--

Device storing the generated

CRC value

D0 2ACFH

Low-order byte CFH

High-order byte 2AH

Contents of target data

Device storing data for which the

CRC value is generated

D100 Low-order byte 30H

D101 Low-order byte 31H

D102 Low-order byte 32H

D103 Low-order byte 33H

D104 Low-order byte 34H

D105 Low-order byte 35H

D106 Low-order byte 36H

Device storing the generated CRC

value

D0 Low-order byte CFH

D1 Low-order byte 2AH

[Structured ladder/FBD] [ST]

M8161:=NOT M8000;

CRC(LDP(TRUE,M0),D100,K7,D0);

M8161

M8000

16-bit

conversion mode

CRC

EN ENO

d

D0D100 s

K7

n

LDP

EN ENO

d

s

M0

[ST]

M8161:=M8000;

LDP(TRUE,M0);

CRC(TRUE,D100,K7,D0);

[Structured ladder/FBD]

8-bit

conversion mode

M8161

M8000

CRC

EN ENO

d

D0D100 s

K7

n

LDP

EN ENO

d

s

M0