12 Applied Instructions (High Speed Processing)

263

FXCPU Structured Programming Manual

[Basic & Applied Instruction]

11

Applied Instructions

(Data Operation)

12

Applied Instructions

(High Speed

Processing)

13

Applied Instructions

(Handy

Instruction)

14

Applied Instructions

(External FX I/O

Device)

15

Applied Instructions

(External Device

(optional device))

16

Applied Instructions

(External Device)

17

Applied Instructions

(Data Transfer 2)

18

Applied Instructions

(Floating Point)

19

Applied Instructions

(Data Operation 2)

20

Applied Instructions

(Positioning

Control)

12.3 MTR / Input Matrix

12.3 MTR / Input Matrix

Outline

This instruction reads matrix input as 8-point input × "n" output (transistor) in the time division method.

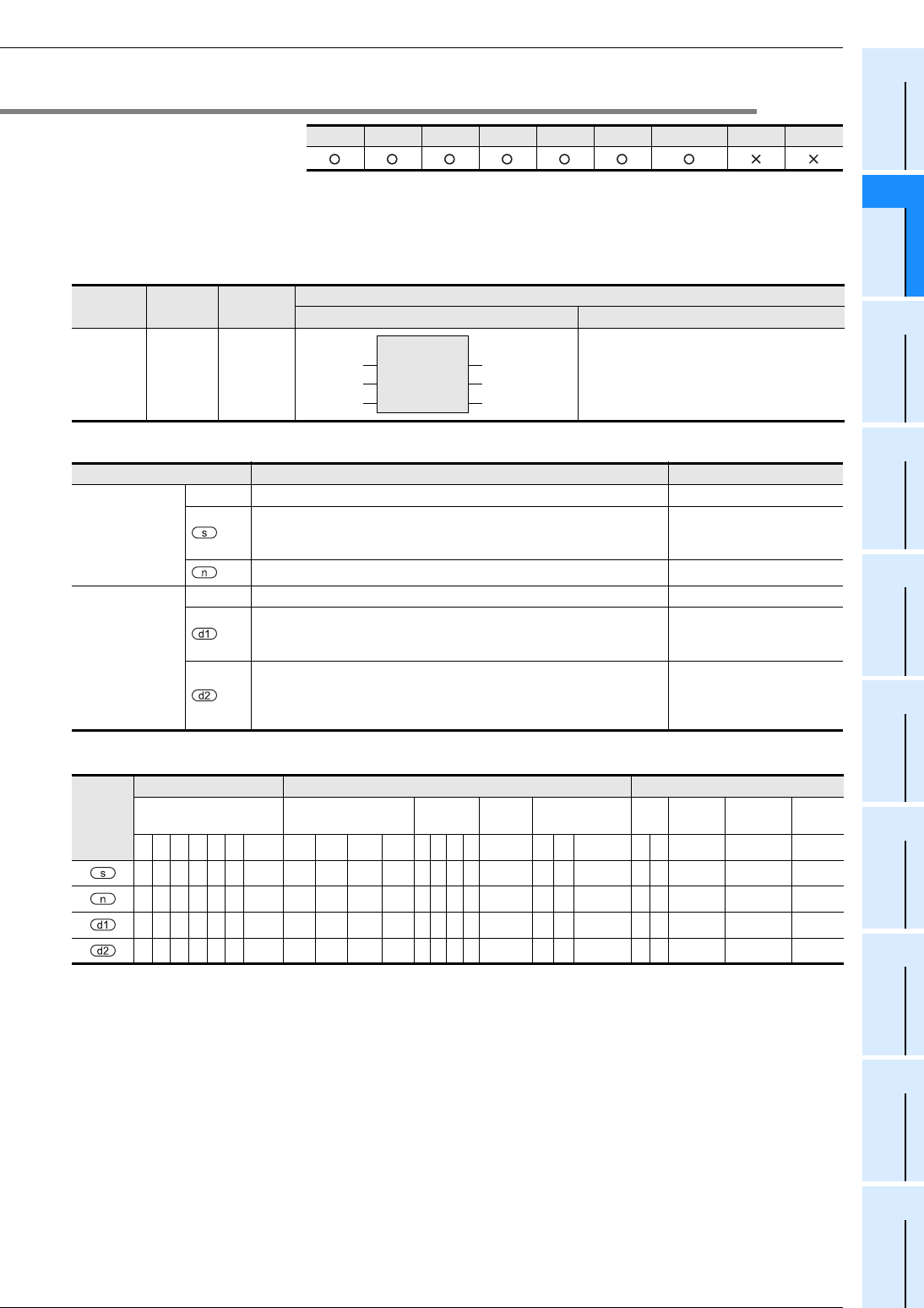

1. Format and operation, execution form

2. Set data

3. Applicable devices

FX3U(C) FX3G(C) FX3S FX2N(C) FX1N(C) FX1S FXU/FX2C FX0N FX0(S)

Instruction

name

Operation

Execution

form

Expression in each language

Structured ladder/FBD ST

MTR 16 bits Continuous MTR(EN, s, n, d1, d2);

Variable Description Data type

Input variable

EN Execution condition Bit

Head device (X) number of matrix signal input

X000, X010, X020, ..., final input X number (Only "0" is allowed in the

least significant digit of device numbers)

Bit

Number of columns in matrix input (K2 to K8/H2 to H8) ANY16

Output variable

ENO Execution state Bit

Head device (Y) number of matrix signal output

Y000, Y010, Y020, ..., final output Y number (Only "0" is allowed in the

least significant digit of device numbers.)

Bit

Head bit device (Y, M or S) number of ON output destination

Y000, Y010, Y020, ..., final Y number, M000, M010, M020, ... , final M

number or S000, S010, S020, ..., final S number (Only "0" is allowed in

the least significant digit of device numbers.)

Bit

Operand

type

Bit Devices Word Devices Others

System User Digit Specification

System

User

Special

Unit

Index

Con

stant

Real

Number

Character

String

Pointer

XYMTCS

D.b

KnX KnY KnM KnS T C D R

U\G

VZModifierKH E

"

"

P

z

zz

z

zz z

MTR

EN

s

n

ENO

d1

d2