396

FX3G/FX3U/FX3UC Series Programmable Controllers

Programming Manual - Basic & Applied Instruction Edition

14 Handy Instruction – FNC 60 to FNC 69

14.2 FNC 61 – SER / Search a Data Stack

14.2 FNC 61 – SER / Search a Data Stack

Outline

This instruction searches for the same data, maximum value and minimum value in a data table.

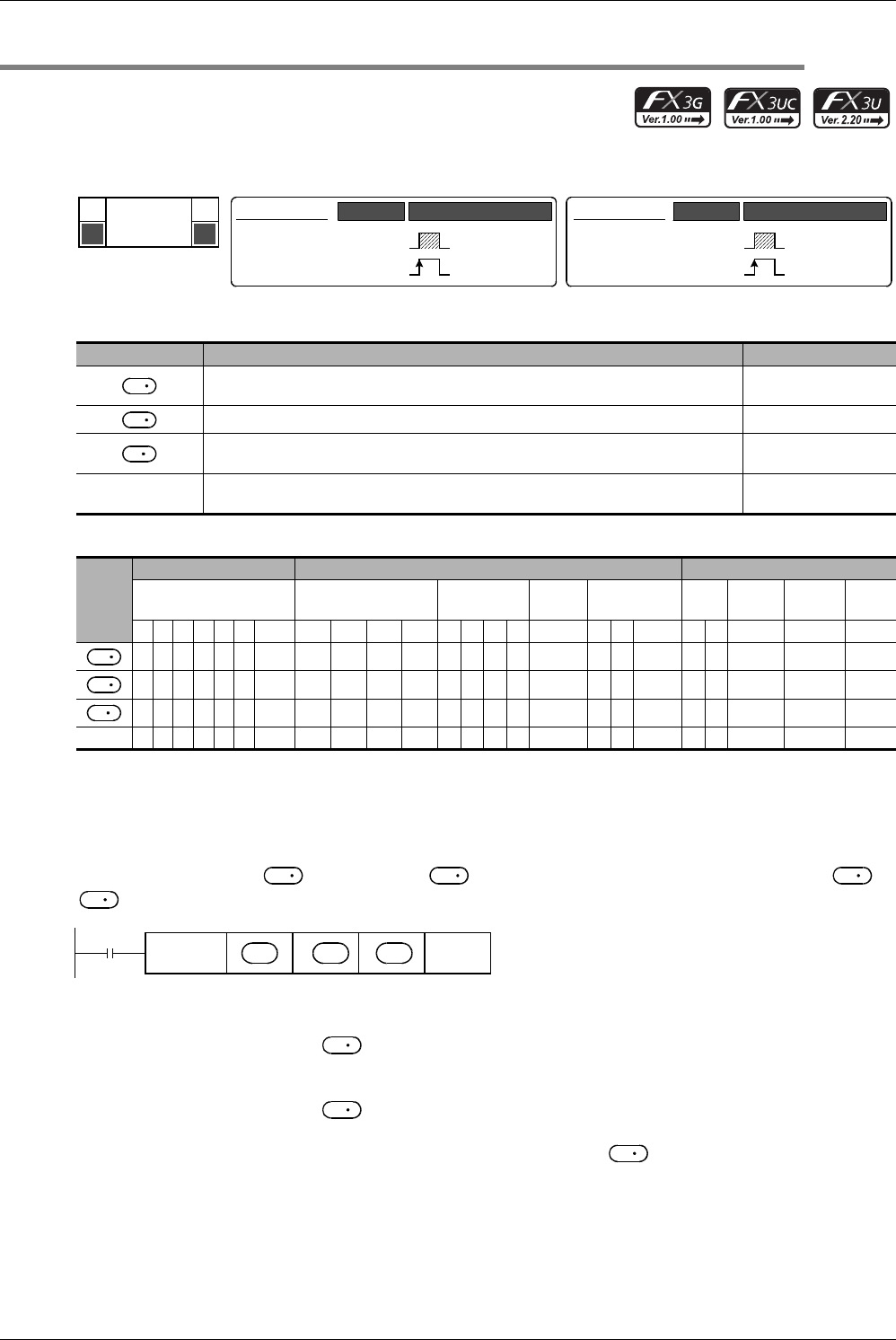

1. Instruction format

2. Set data

3. Applicable devices

S: This function is supported only in FX3U/FX3UC PLCs.

Explanation of function and operation

1. 16-bit operation (SER and SERP)

In "n" data starting from , same data as is searched, and the search result is stored to to

+4.

1) Contents of searched data and the search result

a) When same data was detected

Five devices starting from store the number of same data, first position, last position, maximum value

position and minimum value position.

b) When same data was not detected

Five devices starting from store the number of same data, first position, last position, maximum value

position and minimum value position.

In this case, however, "0" is stored in three devices starting from (which store the number of same

data, first position and last position).

Operand type Description Data type

Head device number in which same data, maximum value and minimum value are

searched

16- or 32-bit binary

Data to be searched for or device number storing data 16- or 32-bit binary

Head device number storing number of same data, maximum value and minimum value

detected by search

16- or 32-bit binary

n

Number of data in which same data, maximum value and minimum value are searched

[16-bit instruction: 1 to 256, 32-bit instruction: 1 to 128]

16- or 32-bit binary

Oper-

and

Type

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index

Con-

stant

Real

Number

Charac-

ter String

Pointer

XYMTCSD

.b KnX KnY KnM KnS T C D R

U\G

V Z Modify K H E "

"P

33333333 S 3

33333333 S 33 3 33

3333333 S 3

n 33 33

DSER

DSERP

Mnemonic Operation Condition

P

FNC 61

SER

D

16-bit Instruction

9 steps

SER

SERP

Mnemonic Operation Condition

Continuous

Operation

Pulse (Single)

Operation

32-bit Instruction

17 steps

Continuous

Operation

Pulse (Single)

Operation

S

1

S

1

S

2

D

S

1

S

1

S

2

S

2

D

S

1

S

2

D

D

Command

input

FNC 61

SER

nS

1

S

2

D

D

D

D