343

FX3G/FX3U/FX3UC Series Programmable Controllers

Programming Manual - Basic & Applied Instruction Edition

13 High Speed Processing – FNC 50 to FNC 59

13.3 FNC 52 – MTR / Input Matrix

11

FNC30-FNC39

Rotation and

Shift

12

FNC40-FNC49

Data Operation

13

FNC50-FNC59

High Speed

Processing

14

FMC60-FNC69

Handy

Instruction

15

FNC70-FNC79

External FX I/O

Device

16

FNC80-FNC89

External FX

Device

17

FNC100-FNC109

Data

Transfer 2

18

FNC110-FNC139

Floating Point

19

FNC140-FNC149

Data

Operation 2

20

FNC150-FNC159

Positioning

Control

13.3 FNC 52 – MTR / Input Matrix

Outline

This instruction reads matrix input as 8-point input × "n"-point output (transistor) in the time division method.

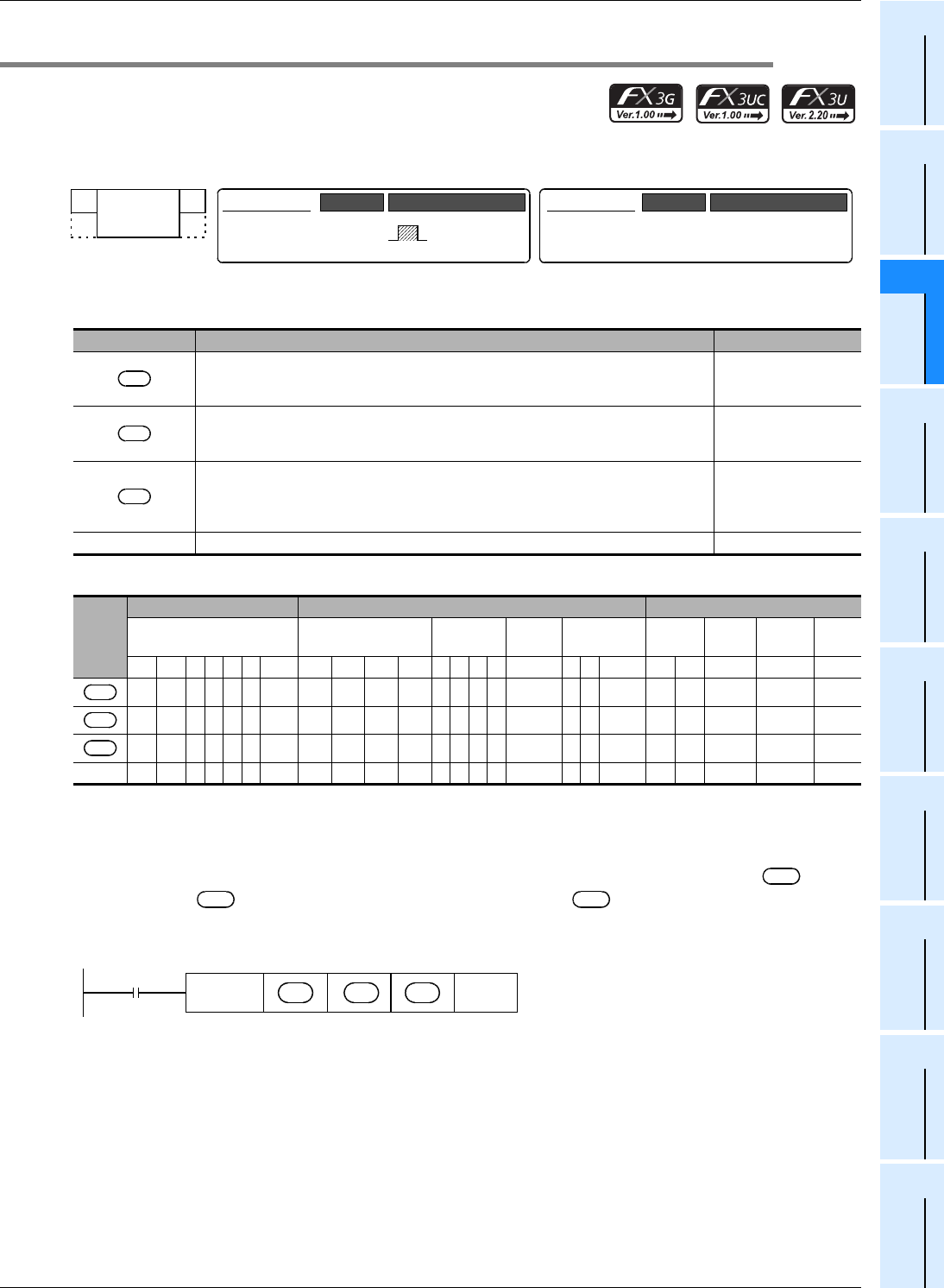

1. Instruction format

2. Set data

3. Applicable devices

Explanation of function and operation

1. 16-bit operation (MTR)

An input signal of 8 points × "n" columns is controlled in the time division method using 8 inputs and "n"

transistor outputs . Each column is read in turn, and then output to .

• For each output, the I/O processing is executed immediately in turn in interrupt at every 20 ms under consideration

of the input filter response delay of 10 ms.

Operand Type Description Data Type

Input device (X) number of matrix signal input

X000, X010, X020 … final input device number

(Only "0" is allowed in the least significant digit of device numbers.)

Bit

Head device (Y) number of matrix signal output

Y000, Y010, Y020 … final output device number

(Only "0" is allowed in the least significant digit of device numbers.)

Bit

Head bit device (Y, M or S) number of ON output destination

Y000, Y010, Y020 … final Y number, M000, M010, M020 … final M number or S000,

S010, S020 … final S number

(Only "0" is allowed in the least significant digit of device numbers.)

Bit

n Number of columns in matrix input (K2 to K8 or H2 to H8) 16-bit binary

Oper-

and

Type

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index Constant

Real

Number

Charac-

ter String

Pointer

XYMTCSD

.b KnX KnY KnM KnS T C D R

U\G

VZModify K H E "

"P

3

3

33 3

n 33

FNC 52

MTR

16-bit Instruction

9 steps

MTR

Mnemonic Operation Condition

Continuous

Operation

−

Mnemonic Operation Condition

32-bit Instruction

S

D

1

D

2

S

D

1

D

2

S

D

1

D

2

Command

input

(normally ON)

FNC 52

MTR

nS D

1

D

2

Number

of

columns

Input

number

Output

number

ON

output

destination