284

FX3G/FX3U/FX3UC Series Programmable Controllers

Programming Manual - Basic & Applied Instruction Edition

10 Arithmetic and Logical Operation (

+

,

−

,

×

,

÷

) – FNC 20 to FNC 29

10.8 FNC 27 – WOR / Logical Word OR

10.8 FNC 27 – WOR / Logical Word OR

Outline

This instruction executes the logical sum (OR) operation of two numeric values.

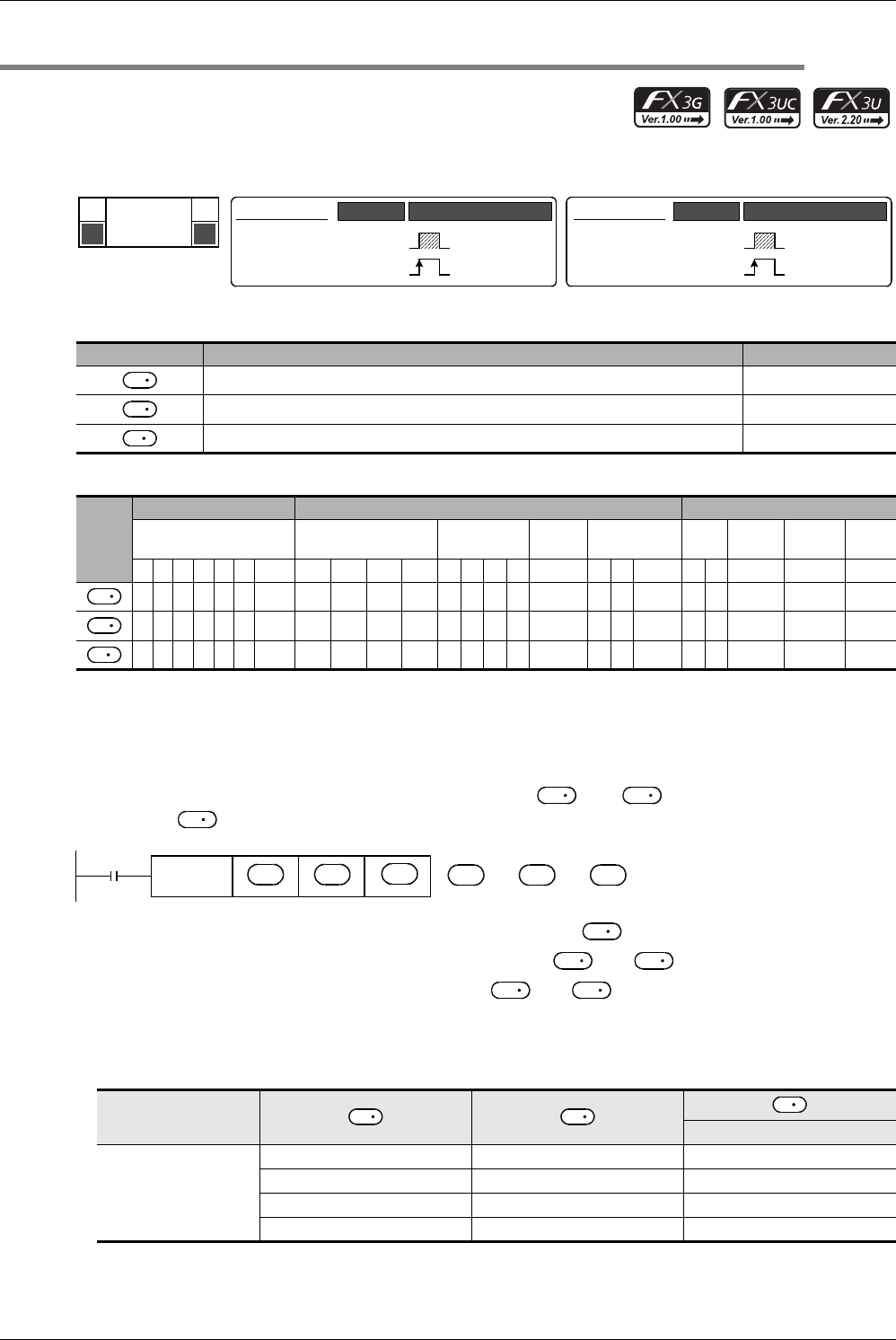

1. Instruction format

2. Set data

3. Applicable devices

S: This function is supported only in FX3U/FX3UC PLCs.

Explanation of function and operation

1. 16-bit operation (WOR and WORP)

The logical sum (OR) operation is executed to the contents of and in units of bit, and the result is

transferred to .

• While the command input is OFF, the data of the transfer destination does not change.

• While the command input is ON, the data of the transfer sources and do not change.

• When a constant (K) is specified in the transfer sources and , it is automatically converted into the

binary format.

• The logical sum operation is executed in units of bit as shown in the table below (1 ∨ 1 = 1, 0 ∨ 1 = 1,

0 ∨ 0 = 0, 1 ∨ 0 = 1).

1: ON, 0: OFF

Operand type Description Data type

Data used for logical sum or word device number storing data 16- or 32-bit binary

Data used for logical sum or word device number storing data 16- or 32-bit binary

Word device number storing the logical sum result 16- or 32-bit binary

Oper-

and

Type

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index

Con-

stant

Real

Number

Charac-

ter String

Pointer

XYMTCSD.b KnX KnY KnM KnS T C D R U\G VZModifyKH E ""P

33333333 S 33 3 33

33333333 S 33 3 33

3333333 S 33 3

WOR (FNC 27) instruction

Logical operation

(unit: bit)

000

101

011

111

DOR

DORP

Mnemonic Operation Condition

W

P

FNC 27

OR

D

16-bit Instruction

7 steps

WOR

WORP

Mnemonic Operation Condition

Continuous

Operation

Pulse (Single)

Operation

32-bit Instruction

13 steps

Continuous

Operation

Pulse (Single)

Operation

S

1

S

2

D

S

1

S

2

D

S

1

S

2

D

Command

input

FNC 27

WOR

S

1

S

2

D

∨

→

S

1

S

2

D

D

S

1

S

2

S

1

S

2

S

1

S

2

D