197

FX3G/FX3U/FX3UC Series Programmable Controllers

Programming Manual - Basic & Applied Instruction Edition

7 Basic Instruction

7.8 MPS, MRD, MPP

1

Introduction

2

Overview

3

Instruction

List

4

Devices

in Detail

5

Specified the

Device &

Constant

6

Before

Programming

7

Basic

Instruction

8

FNC00-FNC09

Program Flow

9

FNC10-FNC19

Move & Compare

10

FNC20-FNC29

Arith. & Logic

Operation

7.8 MPS, MRD, MPP

Outline

FX3G, FX3U and FX3UC PLCs have 11 memories called "Stack" which store the intermediate result (ON or OFF) of

operations.

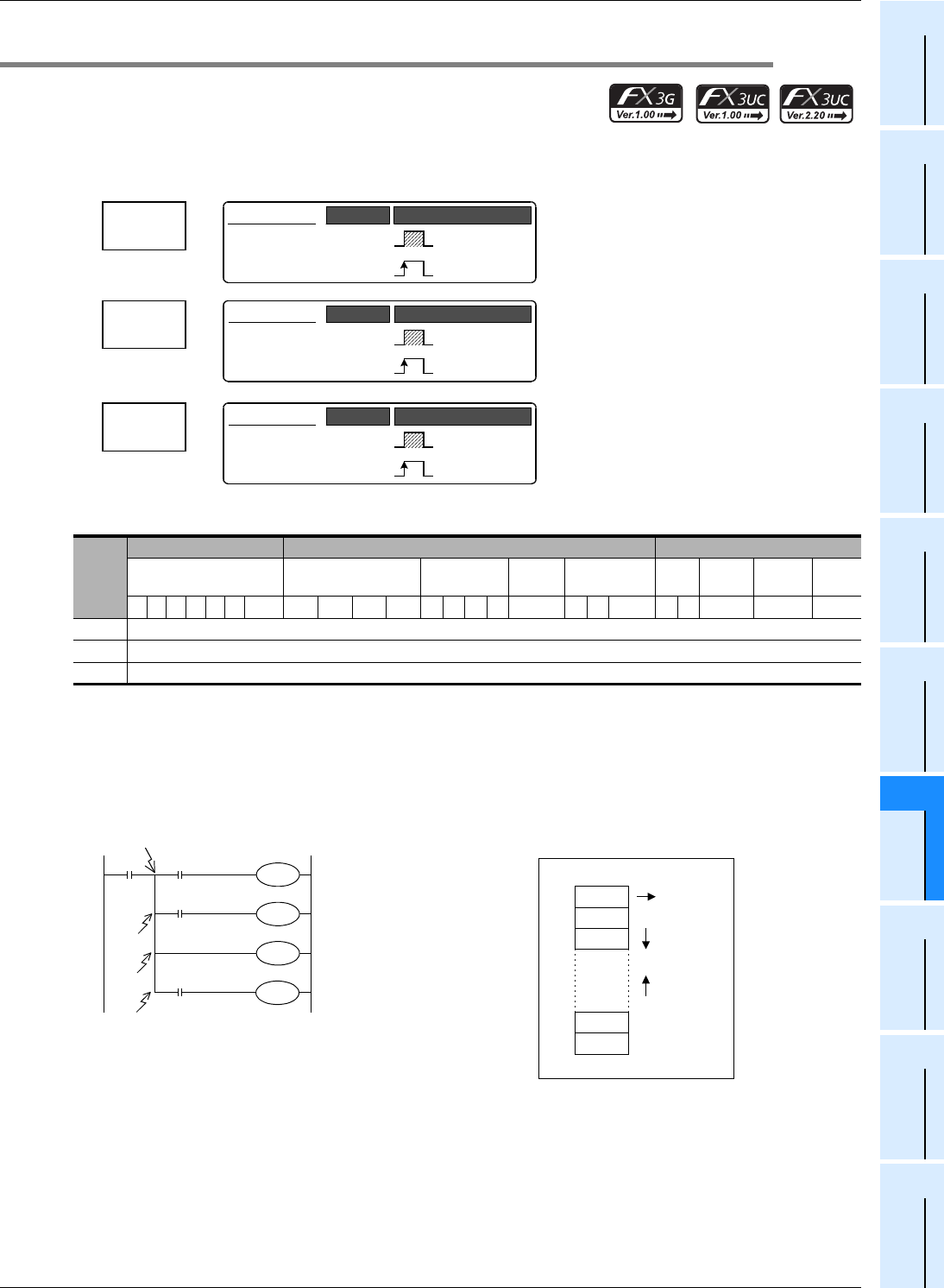

1. Instruction format

2. Applicable devices

Explanation of function and operation

These instructions are convenient in programming branched multi-output circuits.

1. MPS, MRD, and MPP instructions (stores the current result of the internal PLC operations, reads

the current result of the internal PLC operations, and pops (recalls and removes) the currently

stored result)

• Use MPS instruction to store the intermediate result of operation, and then drive the output Y002.

• Use MRD instruction to read the stored data, and then drive the output Y003.

MRD instruction can be programmed as many times as necessary.

• In the final output circuit, use MPP instruction instead of MRD instruction.

MPP instruction reads the stored data described above, and then resets it.

Instruc-

tion

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index

Con-

stant

Real

Number

Charac-

ter String

Pointer

XYMTCSD.b KnX KnY KnM KnS T C D R U\G VZModifyKH E ""P

MPS There are no applicable devices.

MRD There are no applicable devices.

MPP There are no applicable devices.

Memory Point Store

MPS

Basic Instruction

1 step

MPS

−

Continuous

Operation

Pulse (Single)

Operation

Mnemonic Operation Condition

MRD

Memory Read

Basic Instruction

1 step

MRD

−

Continuous

Operation

Pulse (Single)

Operation

Mnemonic Operation Condition

MPP

Memory POP

Basic Instruction

1 step

MPP

−

Continuous

Operation

Pulse (Single)

Operation

Mnemonic Operation Condition

X004 X005

Y002

Y004

X006

Y003

MPS

MRD

MPP

Y005

MRD

[2]

[1]

MPP

MRD

MPS

MPP

Stack

1

2

3

10

11

0018 LD X004

0019

0020 AND X005

0021 OUT Y002

0022

0023 AND X006

0024 OUT Y003

0025

0026 OUT Y004

0027

0028 AND X007

0029 OUT Y005

0030 END

MPS

MRD

MRD

MPP

18

X007