APP - 36

A

PPENDICES

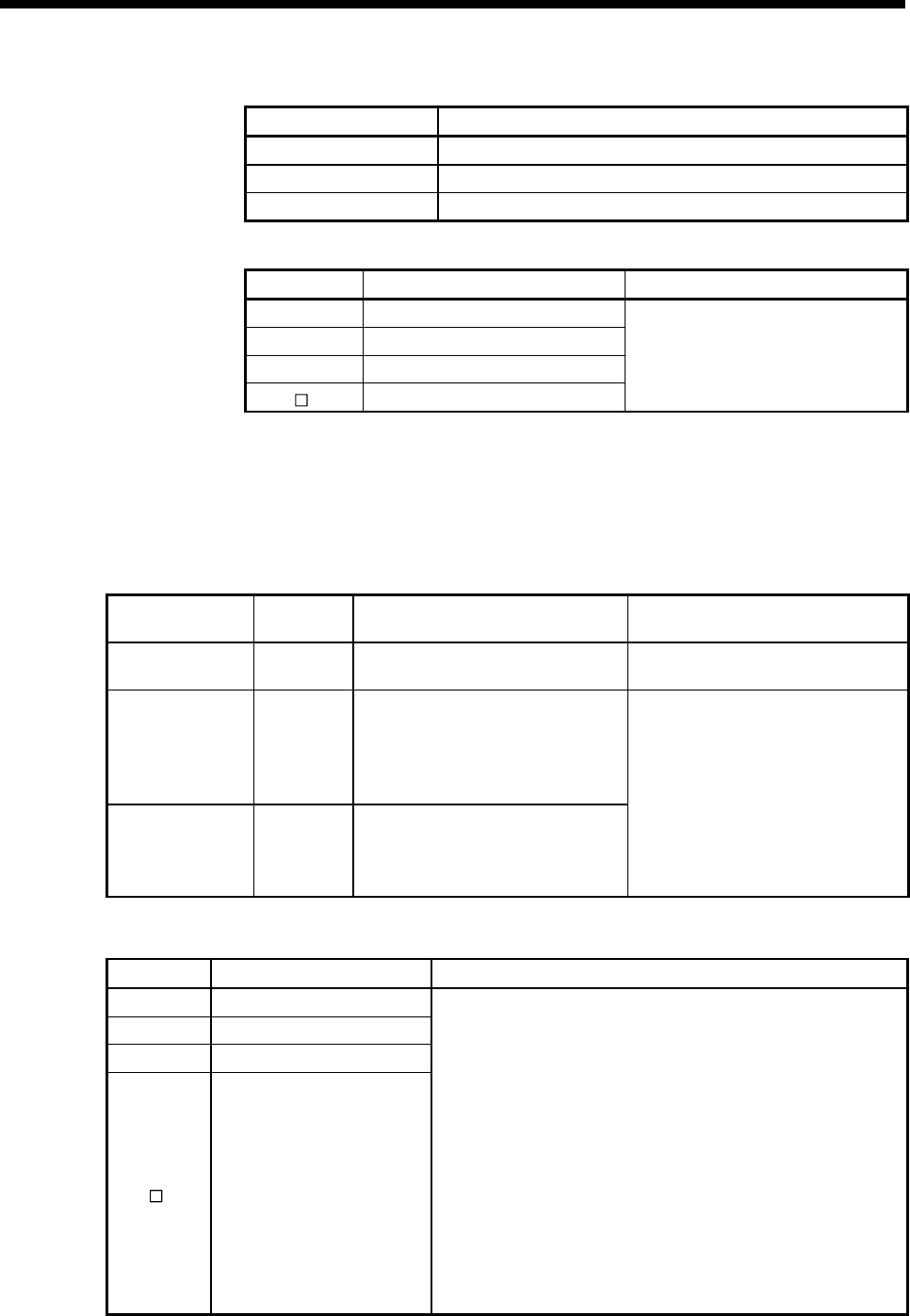

1) Direct designation

Data type Setting range

16-bit integer type K-32768 to K32767, H0000 to HFFFF

32-bit integer type K-2147483648 to K2147483647, H00000000 to HFFFFFFFF

64-bit floating-point type K-1.79E+308 to K-2.23E-308, K0, K2.23E-308 to K1.79E+308

2) Indirect designation

Word device

Setting range

(Note-1)

Remarks

D 0 to 8191

W 0 to 1FFF

# 0 to 9215

U \G

10000 to (10000+p-1)

(Note-2)

The setting value is input for every

operation cycle.

(Note-1): Set an even numbered device in the 32-bit integer type/64-bit floating-point type.

(Note-2): "p" indicates the user setting area points of the Multiple CPU high speed transmission area

for each CPU.

(g) Mark detection mode setting

Set the data storage method of mark detection.

1) Direct designation

Mode

Number of

detections

Operation for mark detection Mark detection data storage method

Continuous

detection mode

— Always

The data is updated in the mark

detection data storage device.

Specified number

of detection mode

1 to 8192

Number of detections

(If the number of mark detections

counter is the number of detections

or more, the mark detection is not

executed.)

Ring buffer mode 1 to 8192

Always

(The mark detection data storage

device is used as a ring buffer for

the number of detections.)

The data is stored in the following

device area.

"Mark detection data storage device

+ Number of mark detections

counter ×Mark detection data size"

2) Indirect designation

Word device Setting range Remarks

D 0 to 8191

W 0 to 1FFF

# 0 to 9215

U \G

10000 to (10000+p-1)

(Note-1)

• Used as 1 word device.

• Set the mark detection mode using the following setting values.

0 : Continuous detection mode

1 to 8192 : Specified number of detection mode

(Use the setting value for the number of

detections.)

-8192 to -1 : Ring buffer mode

(When the value is a negative number, the Ring

Buffer mode is used.)

ex.) -100 means Ring Buffer mode and number

of buffer is 100.

Others : Mark detection : Invalid

• The setting value is input for every operation cycle.

(Note-1): "p" indicates the user setting area points of the Multiple CPU high speed transmission area for each CPU.