Software Developer’s Manual 83

PCI Local Bus Interface

4.1.3 Message Signaled Interrupts

1

Message Signaled Interrupt (MSI) capability is optional for PCI 2.2 or 2.3, but required for PCI-X.

When Message Signaled Interrupts are enabled, instead of asserting an interrupt pin, the Ethernet

controller generates an interrupt using a memory write command. The address and most of the data

of the command are determined by the system and programmed in configuration registers. This

permits the system to program a different message for each function so it can speed up interrupt

delivery.

To enable Message Signaled Interrupts, the system software writes to the “MSI Enable” bit in the

MSI “Message Control” register. When Message Signaled Interrupts are enabled, the Ethernet

controller no longer asserts its INTA# pin to signal interrupts.

MSI systems allow a function to request up to 32 messages, but does not guarantee that all of them

are allocated. The Ethernet controller supports only a single message. When Message Signaled

Interrupts are enabled, the Ethernet controller generates a message when any of the unmasked bits

in the Interrupt Cause Read register (ICR) are set to 1b. The Ethernet controller does not generate

the message again until the ICR is read and a subsequent interrupt event occurs.

In conventional PCI mode, Message Signaled Interrupts can also be disabled in the EEPROM. If

MSI is disabled, the Message Signaled Interrupt registers is not visible.

4.1.3.1 Message Signaled Interrupt Configuration Registers

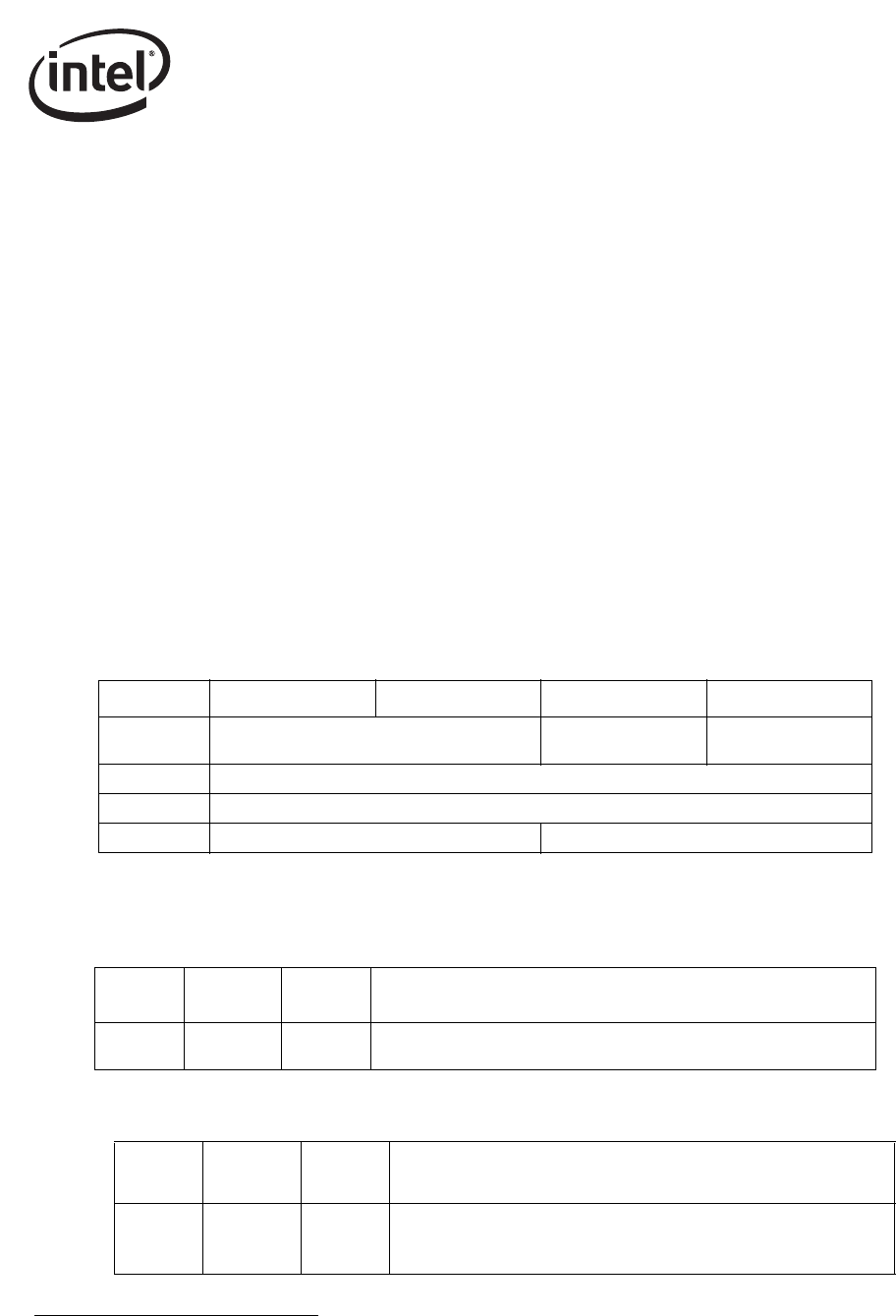

Figure 4-3. Message Signaled Interrupt Configuration Registers

4.1.3.1.1 MSI Capability ID

4.1.3.1.2 Next Capability

1. Not applicable to the 82541xx or 82547GI/EI.

Byte Offset Byte 3 Byte 2 Byte 1 Byte 0

F0h Message Control Next Capability

MSI

Capability ID

F4h Message Address

F8h Message Upper Address

FCh Reserved Message Data

Bits

Read/

Write

Initial

Value

Description

7:0 R 05h

Capability ID - Identifies the Message Signaled Interrupt register set in

the capabilities linked list.

Bits

Read/

Write

Initial

Value

Description

7:0 R 00h

Next Capability – points to the next capability in the capabilities

linked list. Its value is 0b since the Message Signaled Interrupt is the

last item in the list.