Receive and Transmit Description

Software Developer’s Manual 25

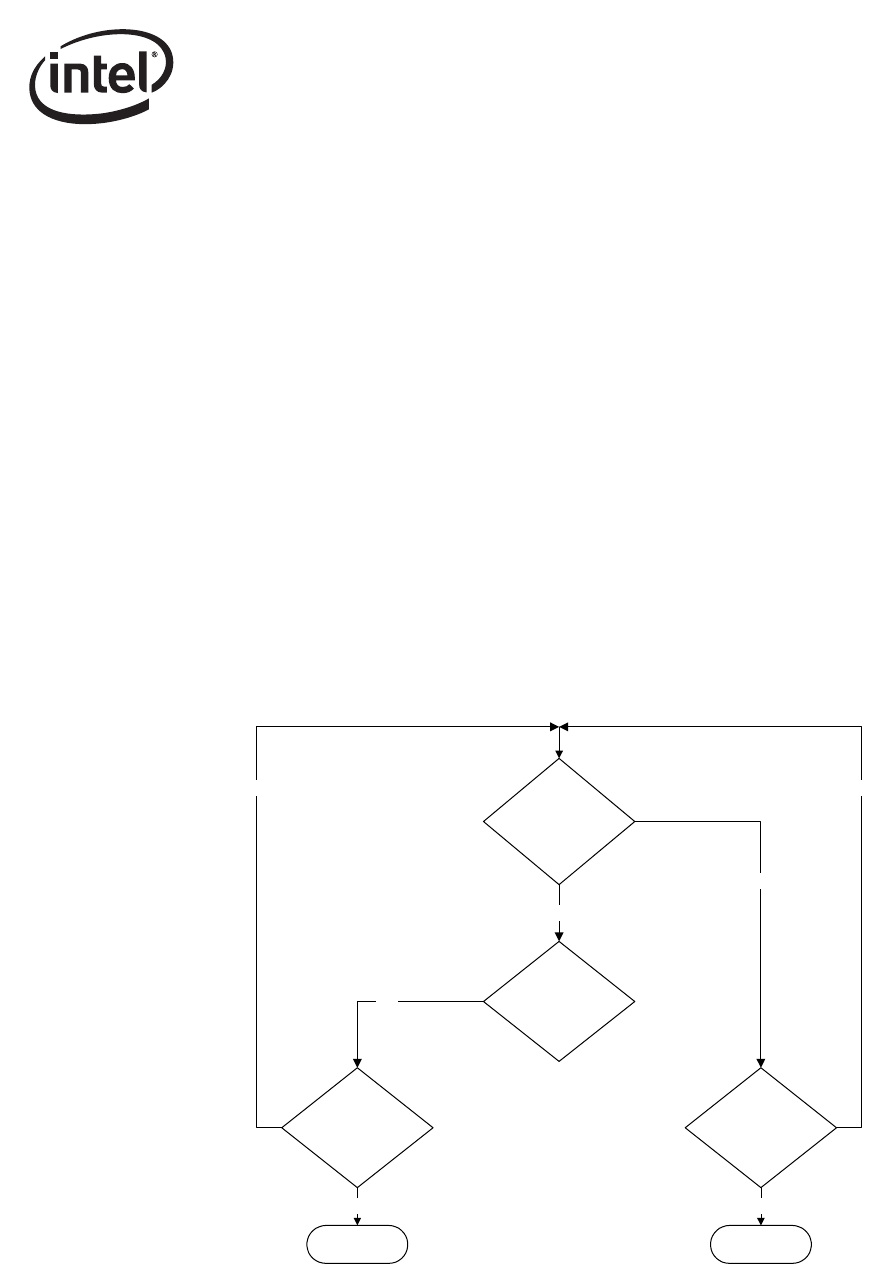

3.2.4 Receive Descriptor Fetching

The descriptor fetching strategy is designed to support large bursts across the PCI bus. This is made

possible by using 64 on-chip receive descriptors and an optimized fetching algorithm. The fetching

algorithm attempts to make the best use of PCI bandwidth by fetching a cache line (or more)

descriptors with each burst. The following paragraphs briefly describe the descriptor fetch

algorithm and the software control provided.

When the on-chip buffer is empty, a fetch happens as soon as any descriptors are made available

(software writes to the tail pointer). When the on-chip buffer is nearly empty

(RXDCTL.PTHRESH), a prefetch is performed whenever enough valid descriptors

(RXDCTL.HTHRESH) are available in host memory and no other PCI activity of greater priority

is pending (descriptor fetches and write-backs or packet data transfers).

When the number of descriptors in host memory is greater than the available on-chip descriptor

storage, the chip may elect to perform a fetch which is not a multiple of cache line size. The

hardware performs this non-aligned fetch if doing so results in the next descriptor fetch being

aligned on a cache line boundary. This mechanism provides the highest efficiency in cases where

fetches fall behind software.

Note: The Ethernet controller never fetches descriptors beyond the descriptor TAIL pointer.

Figure 3-1. Receive Descriptor Fetching Algorithm

On-chip

descriptor cache

is empty

On-chip

descriptor cache <

RDXCTL.PTHRESH

Descriptors

are available in

host memory

Valid descriptors

in host memory >

RXDCTL.HTHRESH

Pre-fetch (based

on PCI priority)

Fetch

No

Yes

Yes

No No

Yes Yes