Software Developer’s Manual 203

Dual Port Characteristics

Dual Port Characteristics 12

12.1 Introduction

1

The 82546GB/EB architecture includes two instances of both the MAC and PHY (see Figure 2-1).

With both MAC/PHY pairs operating, the Ethernet controller appears as a multi-function PCI

device containing two identically-functioning devices. To avoid confusion, each MAC (when

combined with either an internal PHY or an internal TBI transceiver/SerDes) is referred to as

“LANx”, where x = “A” or x = “B” to refer to each logical LAN device (LAN A or LAN B).

This section details specific features common to each MAC or PHY, resources/interfaces for which

dedicated independent hardware/software interfaces exists for each LAN, as well as resources

which are shared by both LAN devices.

The Ethernet controller normally appears to the system as a single, multi-function PCI device. It

provides the ability to selectively disable one of the internal LAN functions, thereby allowing it to

appear to the system as a single-function, single-LAN device. The mechanisms for controlling this

behavior and the resulting appearance to the system are described in Section 12.5 entitled, “LAN

Disable”.

12.2 Features of Each MAC

The Ethernet controller is designed to have the capability to appear as two independent instances of

a gigabit controller. The following section details major features that can be considered to be

distinct features available to each Ethernet controller MAC independently.

12.2.1 PCI/PCI-X interface

The Ethernet controller contains a single physical PCI/PCI-X interface. The Ethernet controller is

designed so that each of the logical LAN devices (LAN A and LAN B) appear as a distinct PCI/

PCI-X bus device implementing, along with other registers, the following PCI device header space:

1. Section 12 only applies to the 82546GB/EB.

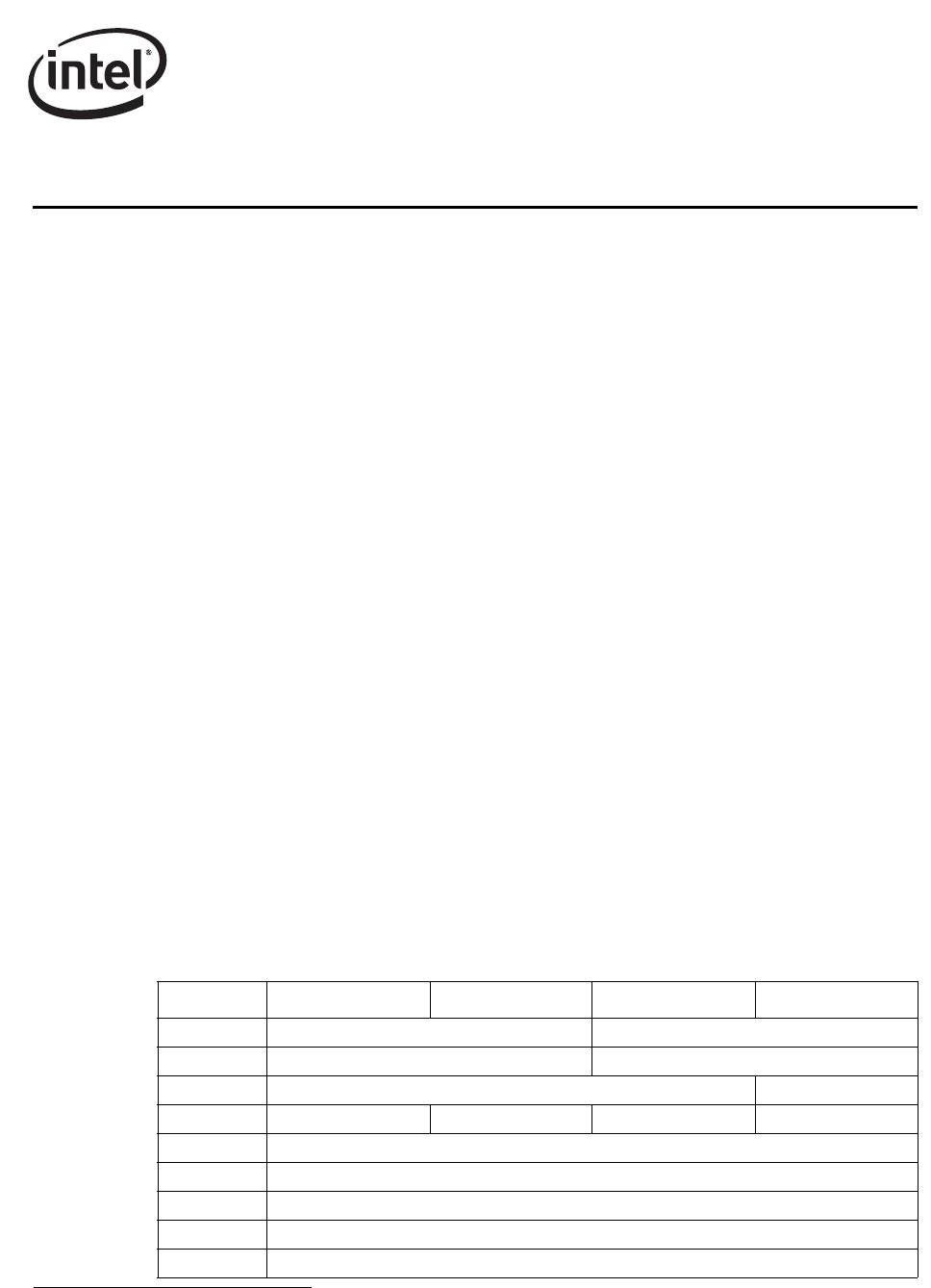

Byte Offset Byte 0 Byte 1 Byte 2 Byte 3

0h Device ID Vendor ID

4h Status Register Command Register

8h Class Code 020000h Revision ID 00h

Ch BIST 00h Header Type 00h Latency Timer Cache Line Size

10h Base Address 0

14h Base Address 1

1h8 Base Address 2

1Ch Base Address 3

20h Base Address 4