Software Developer’s Manual 311

Register Descriptions

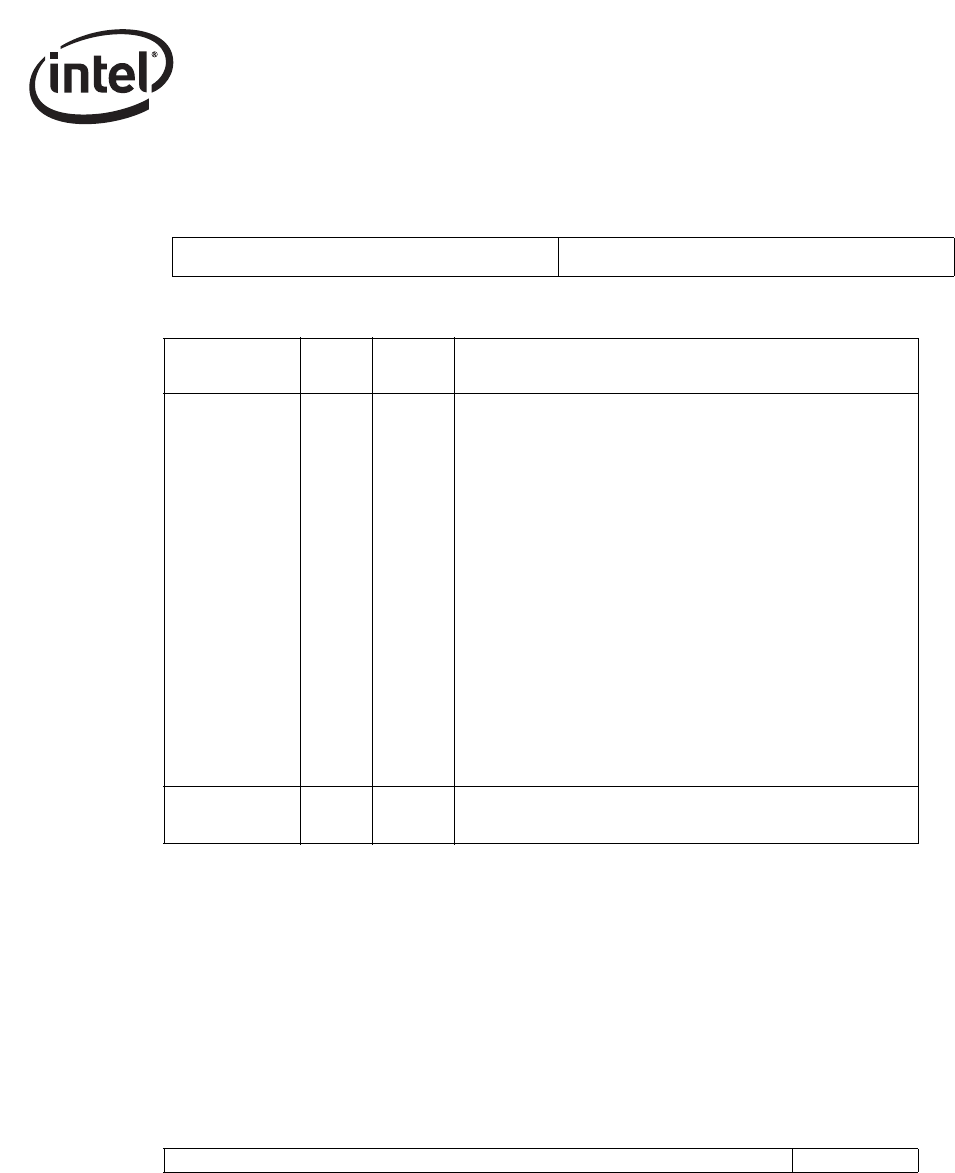

Table 13-78. AIFS Register Bit Description

13.4.36 Transmit Descriptor Base Address Low

TDBAL (03800h; R/W)

This register contains the lower bits of the 64-bit transmit Descriptor base address. The base

register indicates the start of the circular transmit descriptor queue. Since each descriptor is 16 bits

in length, the lower four bits are ignored as the Transmit Descriptor Base Address must point to a

16-byte aligned block of data.

Table 13-79. TDBAL Register Bit Description

31 16 15 0

Reserved Adaptive IFS

Field Bit(s)

Initial

Value

Description

AIFS 15:0 0b

Adaptive IFS Value (82544GC/EI only)

Adaptive IFS throttles back-to-back transmissions in the

transmit packet buffer and delays their transfer to the CSMA/CD

transmit function. Normally, this register should be set to 0b.

However, if additional delay is desired between back-to-back

transmit packets, then this register can be set with a value

greater than zero (0). This feature can be helpful in high collision

half-duplex environments.

In order for AIFS to take effect it should be larger than the

minimum IFS value defined in IEEE 802.3 standard.

AIFS has no effect on transmissions that occur immediately

after receives or transmissions that are not back-to-back. In

addition, it has no effect on re-transmission timing (re-

transmission after collisions).

The AIFS programming value is in units of 8 ns (TX_CLK), and

is 16 bits wide, thus providing greater flexibility and maximum

delay value comparing TIPG.IPGT. The AIFS value is additive to

the TIPG.IPGT value.

Adaptive IFS Value (all remaining Ethernet controllers)

This value is in units of 8 ns.

Reserved 31:16 0b

Reserved

Should be written with 0b.

31 43 0

TDBAL 0