300 Software Developer’s Manual

Register Descriptions

13.4.23 Flow Control Receive Threshold Low

FCRTL (02160h; R/W)

This register contains the receive threshold used to determine when to send an XON packet. It

counts in units of bytes. Each time the receive FIFO crosses the receive high threshold

FCRTH.RTH (filling up), and then crosses the receive low threshold FCRTL.RTL, with

FCRTL.XONE enabled, hardware transmits an XON frame.

Flow control reception/transmission are negotiated capabilities by the Auto-Negotiation process.

When the Ethernet controller is manually configured, flow control operation is determined by the

CTRL.RFCE and CTRL.TFCE bits.

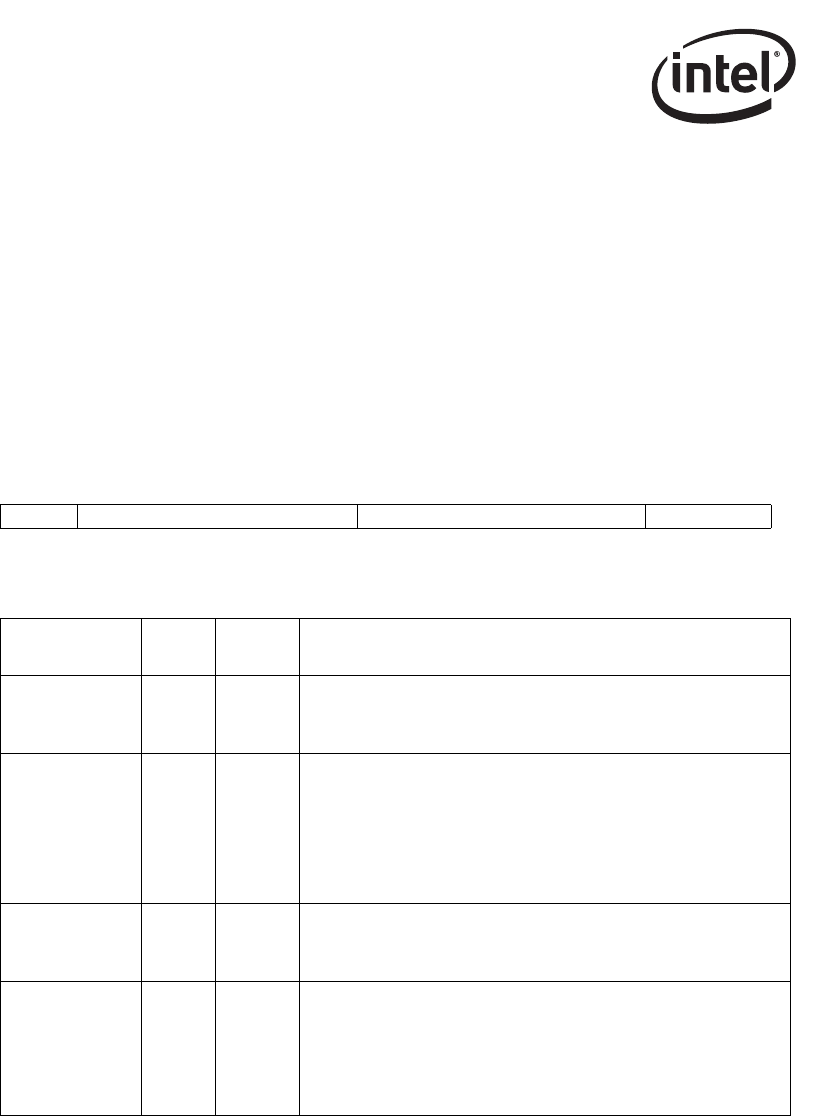

Table 13-68. FCRTL Register Bit Description

31 30 16 15 3 2 0

XONE

1

1. 82544GC/EI, 82541xx, and 82547GI/EI only.

Reserved RTL 0

Field Bit(s)

Initial

Value

Description

Reserved 2:0 0b

Reserved

Should be written with 0b to ensure future compatibility.

Reads as 0b.

RTL 15:3 0b

Receive Threshold Low.

FIFO low water mark for flow control transmission. Each time the

receive FIFO crosses the receive high threshold FCRTH.RTH and

later crosses the receive low threshold FCRTL.RTL with

FCRTL.XONE enabled, hardware transmits an XON frame (a

PAUSE frame with a timer value of 0b).

RTL is provided in units of 8 bytes.

Reserved 31:16 0b

Reserved

Should be written with 0b for future compatibility.

Reads as 0b.

XONE 31 0b

XON Enable (82544GC/EI, 82541xx, and 82547GI/EI only)

0b = Disabled.

1b = Enabled.

When set, enables the Ethernet controller to transmit XON packets

based on receive FIFO crosses FCRTL.RTL threshold value, or

based on external pins XOFF and XON.