Software Developer’s Manual 357

Register Descriptions

All packets received have their octets summed into this register, regardless of their length, whether

they are erred, or whether they are flow control packets. This register includes bytes received in a

packet from the <Destination Address> field through the <CRC> field, inclusively. This register

only increments if receives are enabled.

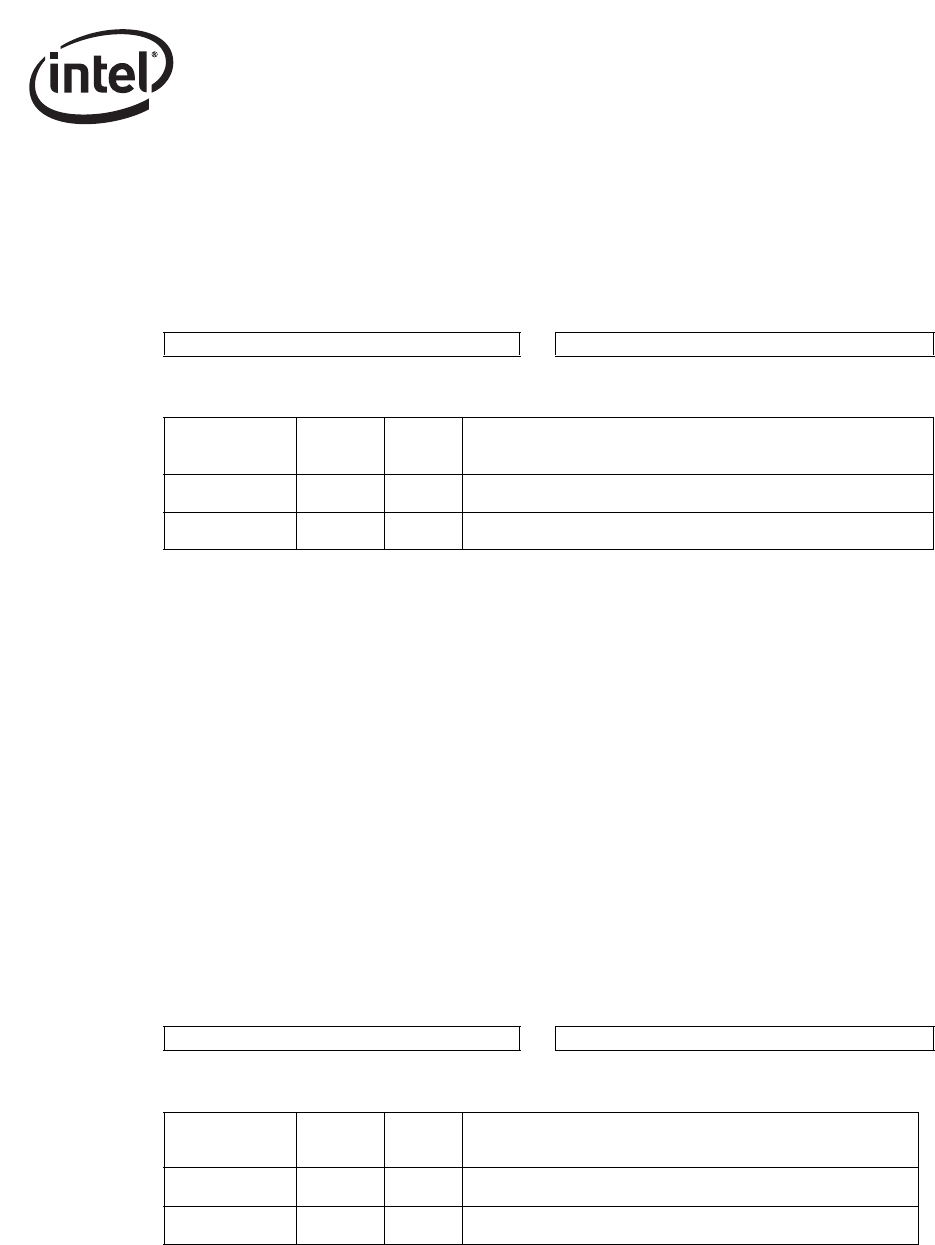

Table 13-130. TORL and TORH Register Bit Descriptions

13.7.42 Total Octets Transmitted

TOTL (040C8h; R/W / TOTH (040CCh; R)

These registers make up a 64-bit register that counts the total number of octets transmitted. This

register resets each time the upper 32 bits are read (TOTH). In addition, it sticks at

FFFF_FFFF_FFFF_FFFFh when the maximum value is reached.

All transmitted packets have their octets summed into this register, regardless of their length or

whether they are flow control packets. This register includes bytes transmitted in a packet from the

<Destination Address> field through the <CRC> field, inclusively.

Octets transmitted as part of partial packet transmissions (collisions in half-duplex mode) are not

included in this register. This register only increments if transmits are enabled.

Table 13-131. TOTL and TOTH Register Bit Descriptions

31 0 31 0

TORH TORL

Field Bit(s)

Initial

Value

Description

TORL 31:0 0b Number of total octets received – lower 4 bytes.

TORH 31:0 0b Number of total octets received – upper 4 bytes.

31 0 31 0

TOTH TOTL

Field Bit(s)

Initial

Value

Description

TOTL 31:0 0b Number of total octets transmitted – lower 4 bytes.

TOTH 31:0 0b Number of total octets transmitted – upper 4 bytes.