Receive and Transmit Description

Software Developer’s Manual 23

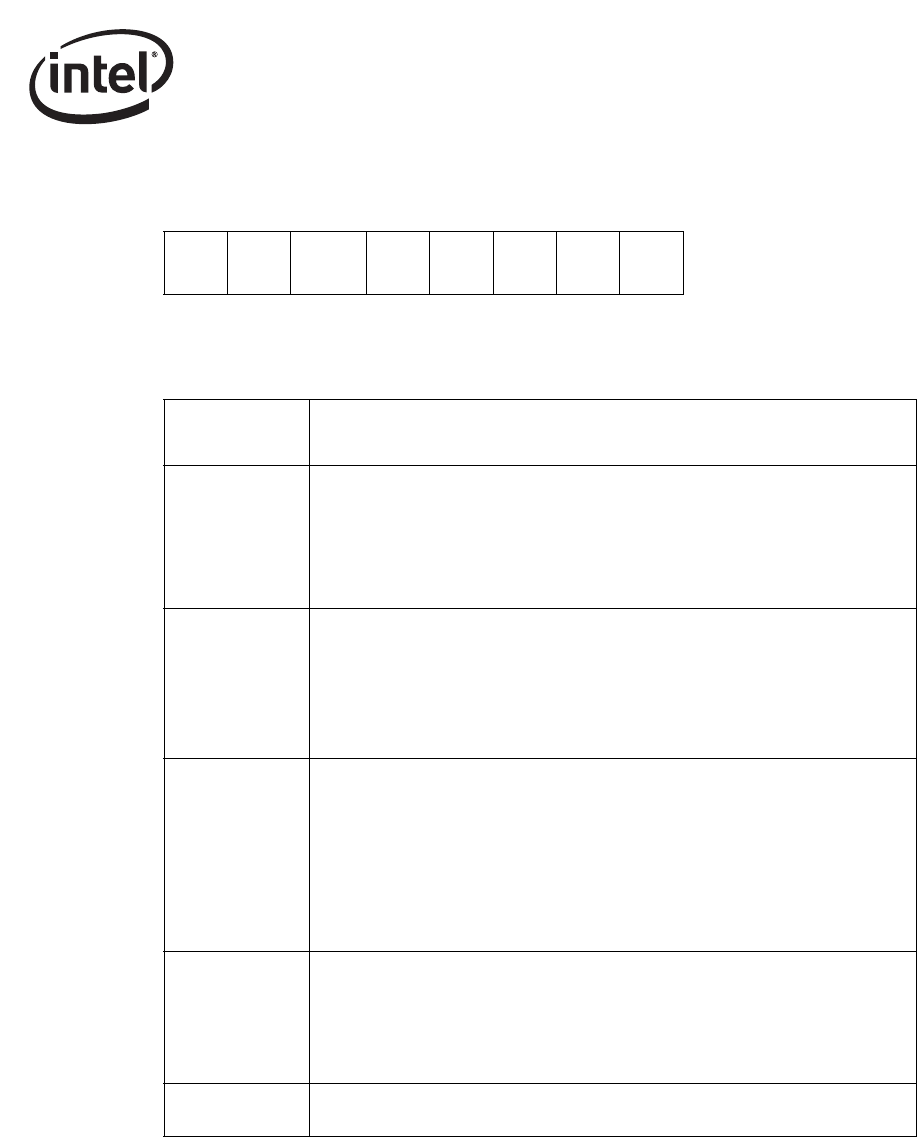

Table 3-3. Receive Errors (RDESC.ERRORS) Layout

76 5 4321 0

RXE IPE TCPE

RSV

CXE

a

a. 82544GC/EI only.

RSV

SEQ

RSV

b

b. 82541xx, 82547GI/EI, and 82540EP/EM only.

SE

RSV

b

CE

Receive

Descriptor Error

bits

Description

RXE (bit 7)

RX Data Error

Indicates that a data error occurred during the packet reception. A data error in TBI

a

mode (82544GC/EI)/internal SerDes (82546GB/EB and 82545GM/EM) refers to the

reception of a /V/ code (see Section 8.2.1.3). In GMII or MII mode, the assertion of

I_RX_ER during data reception indicates a data error. This bit is valid only when the

EOP and DD bits are set; it is not set in descriptors unless RCTL.SBP (Store Bad

Packets) control bit is set.

IPE (bit 6)

IP Checksum Error

When set, indicates that IP checksum error is detected in the received packet. Valid

only when the IP checksum is performed on the receive packet as indicated via the

IPCS bit in the RDESC.STATUS field.

If receive IP checksum offloading is disabled (RXCSUM.IPOFL), the IPE bit is set to

0b. It has no effect on the packet filtering mechanism.

Reads as 0b.

TCPE (bit 5)

TCP/UDP Checksum Error

When set, indicates that TCP/UDP checksum error is detected in the received

packet.

Valid only when the TCP/UDP checksum is performed on the receive packet as

indicated via TCPCS bit in RDESC.STATUS field.

If receive TCP/UDP checksum offloading is disabled (RXCSUM.TUOFL), the TCPE

bit is set to 0b.

It has no effect on the packet filtering mechanism.

Reads as 0b.

CXE

RSV (bit 4)

Carrier Extension Error

When set, indicates a packet was received in which the carrier extension error was

signaled across the GMII interface. A carrier extension error is signaled by the PHY

by the encoding of 1Fh on the receive data inputs while I_RX_ER is asserted.

Valid only while working in 1000 Mb/s half-duplex mode of operation.

This bit is reserved for all Ethernet controllers except the 82544GC/EI.

RSV (Bit 3)

Reserved

Reads as 0b.