Software Developer’s Manual 291

Register Descriptions

Note: The 82547GI/EI signals interrupts over the CSA port, not a dedicated interrupt pin.

13.4.18 Interrupt Throttling Register

1

ITR (000C4h; R/W)

Software can use this register to pace (or even out) the delivery of interrupts to the host CPU. This

register provides a guaranteed inter-interrupt delay between interrupts asserted by the Ethernet

controller, regardless of network traffic conditions. To independently validate configuration

settings, software can use the following algorithm to convert the inter-interrupt interval value to the

common interrupts/sec performance metric:

For example, if the interval is programmed to 500d, the Ethernet controller guarantees the CPU is

not interrupted by the Ethernet controller for 128

µsec from the last interrupt. The maximum

observable interrupt rate from the Ethernet controller must never exceed 7813 interrupts/sec.

Inversely, inter-interrupt interval value can be calculated as:

The optimal performance setting for this register is very system and configuration specific. A

initial suggested range is 651-5580 (28Bh - 15CCh).

Reserved 31:17 0b

Reserved

Reads as 0b.

1. The 82540EP/EM, 82541xx, or 82547GI/EI do not support SerDes functionality.

2. Not applicable to the 82544GC/EI.

1. Not applicable to the 82544GC/EI.

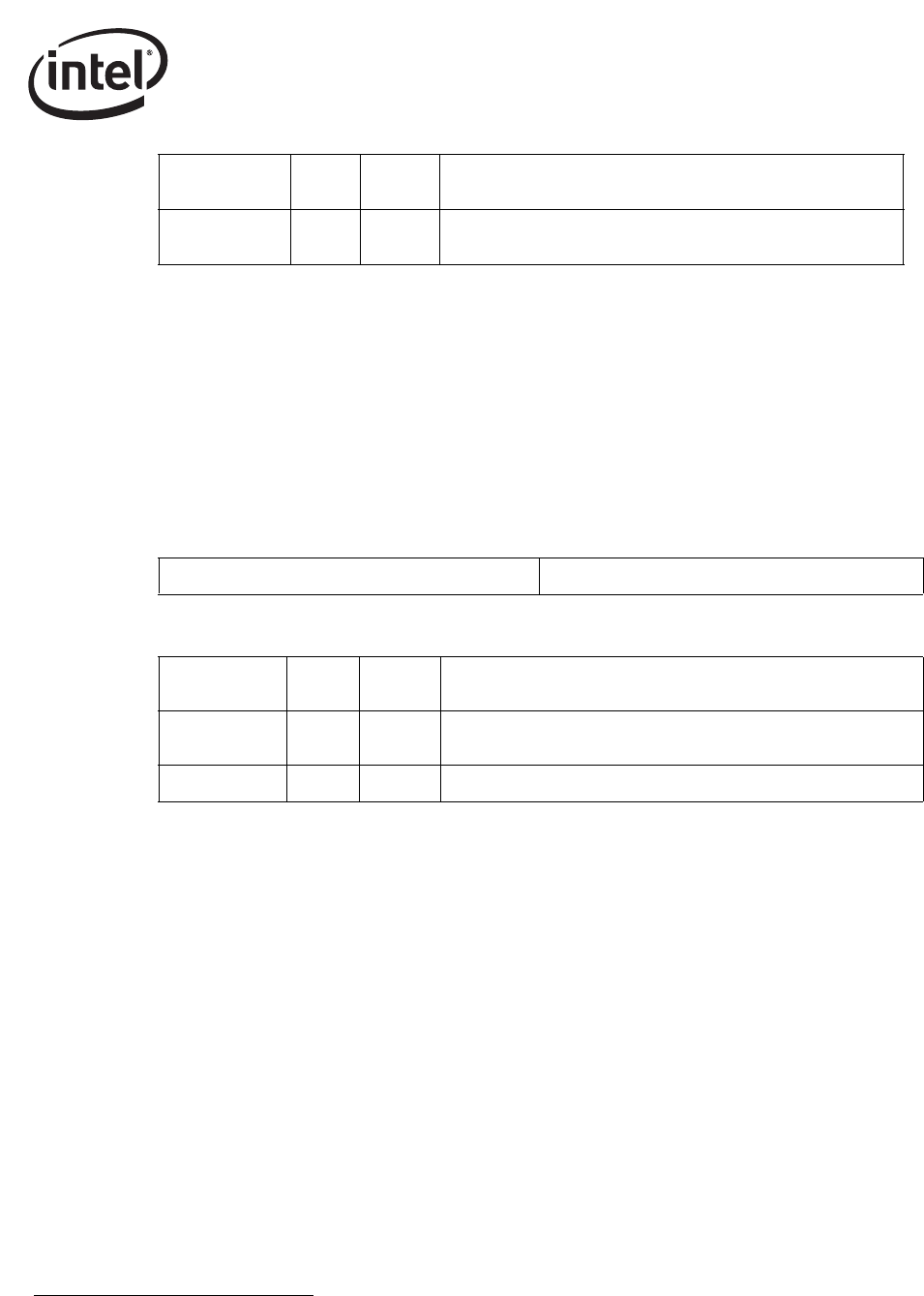

Field Bit(s)

Initial

Value

Description

31 - 16 15 - 0

Reserved INTERVAL

Field Bit(s)

Initial

Value

Description

INTERVAL 15:0 0b

Minimum inter-interrupt interval. The interval is specified in 256 ns

increments. Setting this bit to 0b disables interrupt throttling logic.

Reserved 31:16 X Reserved. Should be written with 0b to ensure future compatibility.

interrupts/ ondsec 256

9–

×10 interval×()

1–

=

inter-interrupt interval 256

9–

×10 interrupts/sec×()

1–

=