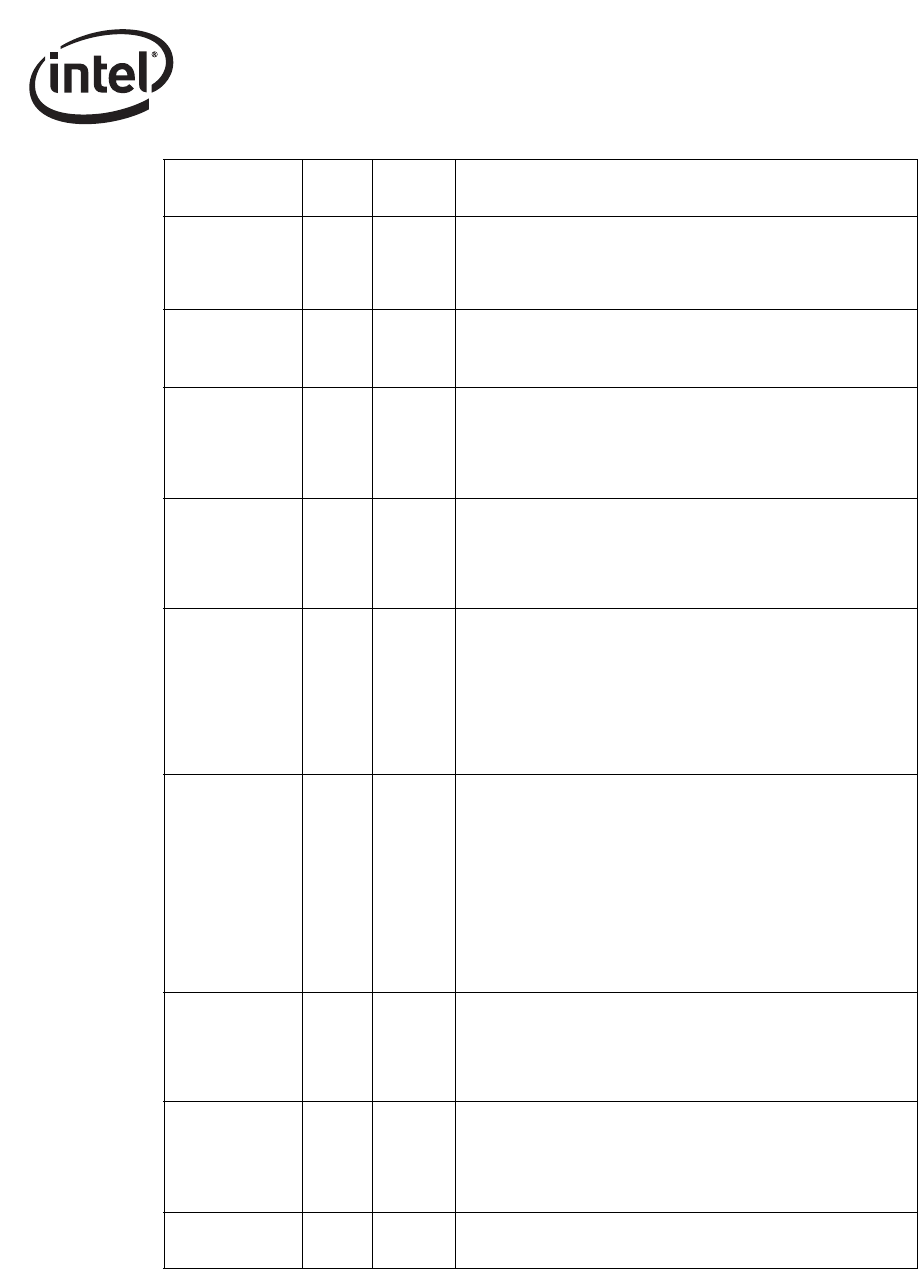

Software Developer’s Manual 223

Register Descriptions

FRCDPLX 12 0b

Force Duplex

When set, software can override the duplex indication from the

PHY which is in internal PHY mode. When set the CTRL.FD bit

sets duplex. When cleared, the CTRL.FD is ignored.

Reserved 17:13 0b

Reserved

Should be written with 0b to ensure future compatibility.

Read as 0b

SDP0_DATA 18 0b

2

SDP0 Data Value. Used to read (write) value of software-

controllable IO pin SDP0. If SDP0 is configured as an output

(SDP0_IODIR=1b), this bit controls the value driven on the pin

(initial value EEPROM-configurable). If SDP0 is configured as

an input, reads return the current value of the pin.

SDP1_DATA 19 0b

2

SDP1 Data Value. Used to read (write) value of software-

controllable IO pin SDP1. If SDP1 is configured as an output

(SDP1_IODIR=1b), this bit controls the value driven on the pin

(initial value EEPROM-configurable). If SDP1 is configured as

an input, reads return the current value of the pin.

ADVD3WUC 20 0b

2

D3Cold Wakeup Capability Advertisement Enable. When set,

D3Cold wakeup capability is advertised based on whether the

AUX_PWR pin advertises presence of auxiliary power (yes if

AUX_PWR is indicated, no otherwise). When 0b, however,

D3Cold wakeup capability is not advertised even if AUX_PWR

presence is indicated. Formerly used as SDP2 pin data value,

initial value is EEPROM-configurable.

Note: Not applicable to the 82541ER.

EN_PHY_

PWR_MGMT

21

0b

2

1b

1

PHY Power-Management Enable. When set, the PHY is

informed of power-state transitions and attempts to auto-

negotiate advertising lower line speeds only (10 or 100 Mb/sec)

when entering D3 or D0u power states with wakeup or

manageability enabled. It again re-negotiates, advertising full

speed capabilities (10/100/1000 Mbps) when transitioning back

to full D0 operational state. If this bit is clear, the PHY automatic

speed/power management capability is disabled, and the PHY

remains operational at its current line speed through power-

state transitions. Formerly used as SDP3 pin data value, initial

value is EEPROM-configurable.

SDP0_IODIR 22 0b

2

SDP0 Pin Directionality. Controls whether software-controllable

pin SDP0 is configured as an input or output (0b = input, 1b =

output). Initial value is EEPROM-configurable. This bit is not

affected by software or system reset, only by initial power-on or

direct software writes.

SDP1_IODIR 23 0b

2

SDP1 Pin Directionality. Controls whether software-controllable

pin SDP1 is configured as an input or output (0b = input, 1b =

output). Initial value is EEPROM-configurable. This bit is not

affected by software or system reset, only by initial power-on or

direct software writes.

Reserved 25:24 0b

Reserved. Formerly used as SDP2and SDP3 pin input/output

direction control.

Field Bit(s)

Initial

Value

Description