Software Developer’s Manual 249

Register Descriptions

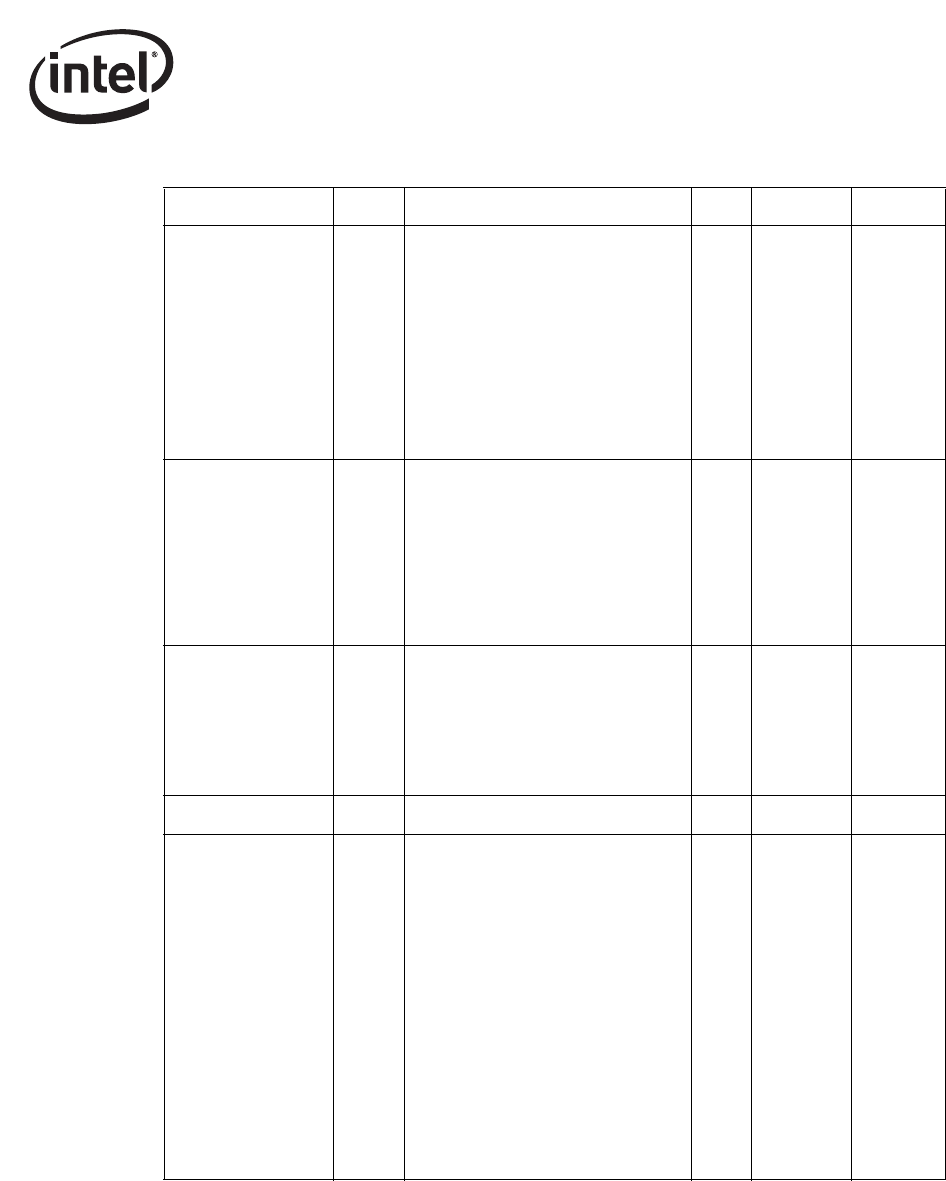

Asymmetric Pause

ASM_DIR for the

(82541xx and

82547GI/EI)

11

1b = Asymmetric Pause.

0b = No asymmetric Pause.

Values programmed in the Auto-

Negotiation advertisement register

have no effect unless Auto-

Negotiation is restarted (PHY Control

Register) or link goes down.

82541xx and 82547GI/EI only:

Advertise Asymmetric Pause direction

bit. This bit is used in conjunction with

PAUSE.

R/W

0b

1b for the

(82541xx

and

82547GI/

EI)

Retain

Reserved 12

This bit is reserved and equals 0b.

Values programmed in the Auto-

Negotiation advertisement register

have no effect unless Auto-

Negotiation is restarted (PHY Control

Register) or link goes down.

Reserved bit is R/W to allow for

forward compatibility with future IEEE

standards.

R/W 0b Retain

Remote Fault 13

1b = Set Remote Fault bit.

0b = Do not set Remote Fault bit.

Values programmed in the Auto-

Negotiation advertisement register

have no effect unless Auto-

Negotiation is restarted (PHY Control

Register) or link goes down.

R/W 0b Retain

Reserved 14 Reserved. Should be set to 0b. RO Always 0b

Next Page 15

1b = Advertise.

0b = Not advertised.

Values programmed in the Auto-

Negotiation advertisement register

have no effect unless Auto-

Negotiation is restarted (PHY Control

Register) or link goes down.

If 1000BASE-T is advertised then the

required next pages are automatically

transmitted. The Next Page bit should

equal 0 if no additional next pages are

needed.

82541xx and 82547GI/EI only:

1b = Manual control of Next Page

(Software).

0b = Ethernet controller control of Next

Page (Auto).

R/W 0b Retain

1. For the 82541xx and 82547GI/EI, if EEPROM bit ADV10LU is asserted, then the default is set to 0b. Otherwise, the default

is 1b.

Table 13-20. Auto-Negotiation Advertisement Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst