194 Software Developer’s Manual

PHY Functionality and Features

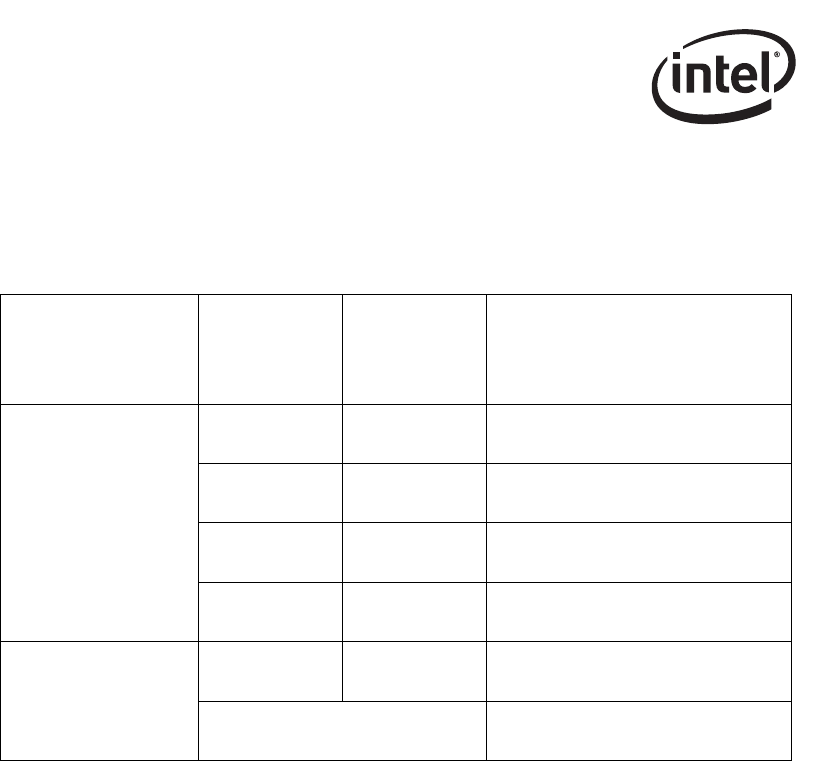

Table 10-2 lists the intended operation for the various settings of ASM_DIR and Pause. This

information is provided for reference only; it is the responsibility of the MAC to implement the

correct function. The PHY merely enables the two MACs to communicate their abilities to each

other.

11.9 Management Data Interface

The PHY supports the IEEE 802.3 MII Management Interface also known as the Management

Data Input/Output (MDIO) Interface. The MDIO interface consists of a physical connection to the

MAC, a specific protocol which runs across the connection, and a 16-bit MDIO register set.

PHY Registers 0d through 10d and 15d are required and their functions are specified by the IEEE

802.3 specification. Additional registers are included for expanded functionality.

11.10 Low Power Operation

The Ethernet controller can be get into a low-power state according to MAC control (Power

Management controls) or via PHY register 0d. In either power down mode, the Ethernet controller

is not capable of receiving or transmitting packets.

Table 10-2. Pause And Asymmetric Pause Settings

ASM_DIR Settings

Local

(PHY Register 4d, Bit

10) and Remote (PHY

Register 5d, Bit 10)

Pause Setting -

Local (PHY

Register 4d, Bit

9)

Pause Setting -

Remote (PHY

Register 5d, Bit

9)

Result

Both ASM_DIR = 1b

1b 1b

Symmetric - Either side can flow control

the other

1b 0b

Asymmetric - Remote can flow control

local only

0b 1b

Asymmetric - Local can flow control

remote

0b 0b No flow control

Either or both

ASM_DIR = 0b

1b 1b

Symmetric - Either side can flow control

the other

Either or both = 0b No flow control