Software Developer’s Manual 279

Register Descriptions

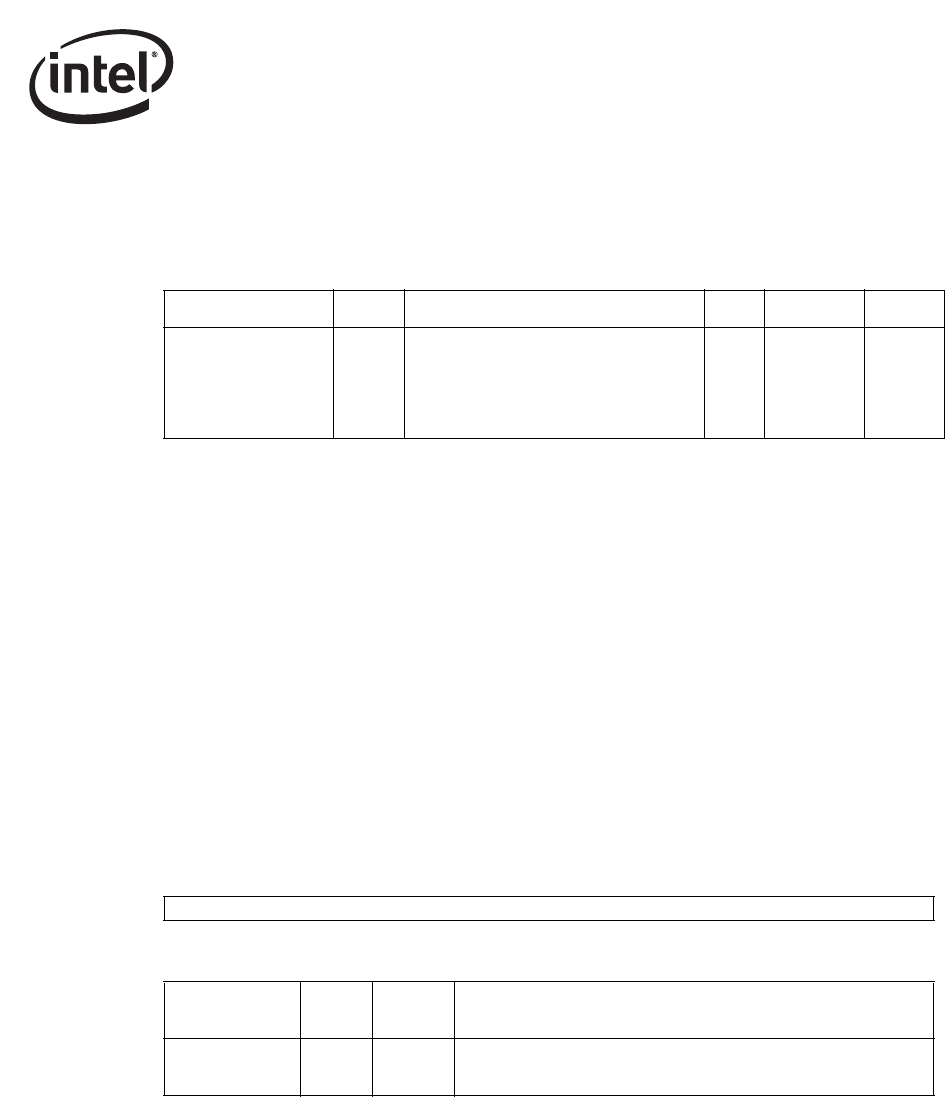

13.4.7.1.28 PHY Page Select Register (82541xx and 82547GI/EI Only)

PPAGE (31d; R/W)

13.4.8 Flow Control Address Low

FCAL (00028h; R/W)

Flow control packets are defined by IEEE 802.3x to be either a unique multicast address or the

station address with the EtherType field indicating PAUSE. The FCAL, FCAH registers provide

the value hardware compares incoming packets against to determine that it should PAUSE its

output, and hardware use when transmit PAUSE packets to its remote node when flow control is

activated.

The FCAL register contains the lower bits of the internal 48-bit Flow Control Ethernet address. All

32 bits are valid. Software can access the High and Low registers as a register pair if it can perform

a 64-bit access to the PCI bus. This register should be programmed with 00_C2_80_01h. The

complete flow control multicast address is: 01_80_C2_00_00_01h; where 01h is the first byte on

the wire, 80h is the second, etc.

Table 13-53. FCAL Register Bit Description

13.4.9 Flow Control Address High

FCAH (0002Ch; R/W)

This register contains the upper bits of the 48-bit Flow Control Ethernet address. Only the lower 16

bits of this register have meaning. The complete Flow Control address is {FCAH, FCAL}. This

register should be programmed with 01_00h. The complete flow control multicast address is:

01_80_C2_00_00_01h; where 01h is the first byte on the wire, 80h is the second, etc.

Table 13-52. PHY Page Select Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

PAGE_SEL 15:0

This register is used to swap out the

Base Page containing the IEEE

registers for Intel reserved test and

debug pages residing within the

Extended Address space.

WO 0b 0b

31 0

FCAL

Field Bit(s)

Initial

Value

Description

FCAL 31:0 X

Flow Control Address Low

Should be programmed with 00_C2_80_01h