Software Developer’s Manual 207

Dual Port Characteristics

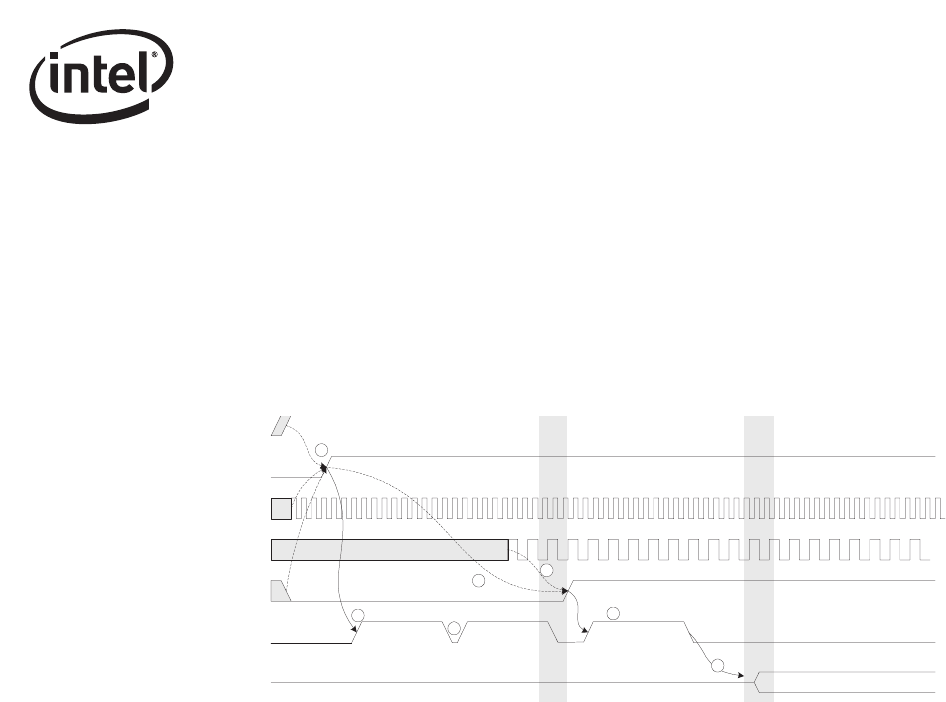

The result of multiple LAN devices’ reading EEPROM is that power-on and reset-initiated

EEPROM read sequences might appear slightly differently from the sequences illustrated during

the discussion of power-state transitions (Section 6.3.2). Those illustrations indicate EEPROM

read periods without distinguishing between reads by LAN A versus LAN B devices. At initial

power-on, both LAN devices always execute an EEPROM read sequence. However, since the

enabling/disabling of a particular LAN device occurs on the deassertion of PCI reset, the post-reset

EEPROM read sequence(s) are only performed by LAN device(s) that are enabled. The following

illustration more clearly illustrates the EEPROM read sequence for a scenario where a single LAN

device is enabled:

12.4 Shared FLASH

The Ethernet controller provides an interface to an external FLASH/ROM memory device, as

described in Section 7. This FLASH/ROM device can be mapped into memory and/or I/O address

space for each LAN device through the use of PCI Base Address Registers (BARs). Bit 3 of the

EEPROM Initialization Control Word 3 associated with each LAN device selectively disables/

enables whether the FLASH can be mapped for each LAN device by controlling the BAR register

advertisement and writeability.

12.4.1 FLASH Access Contention

Unlike the shared EEPROM implementation, the Ethernet controller does NOT implement any

internal arbitration between FLASH accesses initiated through the LAN A device and those

initiated through the LAN B device. If accesses from both LAN devices are initiated during the

same approximate time window, access contention can occur. If contention occurs, the external

FLASH addresses can be corrupted or unstable throughout the access. During writes to FLASH,

contention can result in corrupt or unstable data values; contention during reads can result in

erroneous read data being returned.

EEPROM read,

LAN

A device

9

Running

3

t

eepci

t

ee

6

5

3

t

clkpr

t

pgrst

t

pree

EEPROM read,

LAN

EEPROM read,

LAN

A device

B device

EEPROM read,

LAN

A device

2

t

ee

t

pgee

PCI Pins

Reading EEPROM

RST#

CLK

125 MHz XTAL IN

t

txpg

t

ppg

1

Power

LAN_PWR_GOOD