Software Developer’s Manual 189

PHY Functionality and Features

11.5 Initialization

Note: Section 11.5 through Section 11.14 apply only to the 82541xx and 82547GI/EI Ethernet

controllers.

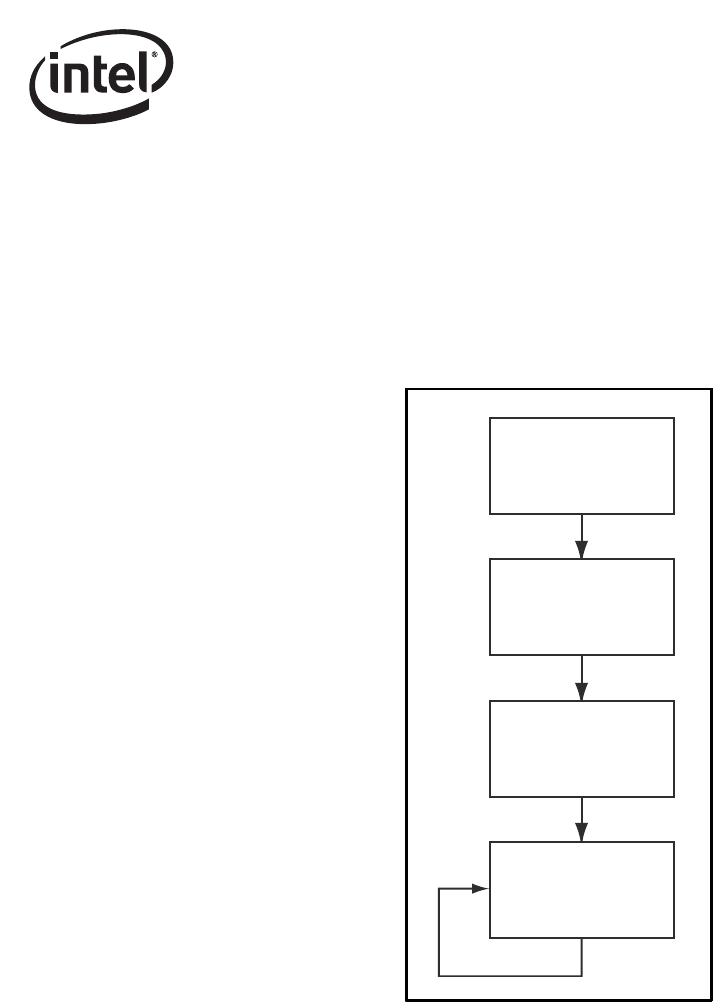

At power-up or reset, the PHY core performs the initialization as shown in Figure 11-1. The

software driver has access to the PHY register 0d, bits 15 and 11 for PHY reset and PHY Power

Down control, respectively.

Figure 11-1. PHY Initialization Sequence

11.5.1 MDIO Control Mode

In the MDIO Control mode, the PHY uses the Hardware Control Interface to set up initial (default)

values of the MDIO registers. Once initial values are set, bit control reverts to the MDIO interface.

The PHY can perform some low level initializations such as DSP configuration based upon

EEPROM settings. The details of those initializations are reserved.

Power-up

or

Reset

Read H/W

Control

Interface

Initialize

MDIO

Registers

Pass control

to

MDIO Interface