Software Developer’s Manual 109

EEPROM Interface

5.6.13 PHY Register Address Data (Words 10h, 11h, and 13h - 1Eh)

These settings are specific to individual platform configurations for the 82541xx and 82547GI/EI

and should not be altered from the reference design unless instructed to do so. Future Intel Ethernet

controllers might use this space differently.

5.6.14 OEM Reserved Words (Words 10h, 11h, 13h - 1Fh)

Words 10h, 11h, and 13h through 1Fh of the EEPROM are reserved areas for general OEM use for

all Ethernet controllers except the 82546GB/EB.

5.6.15 EEPROM Size (Word 12h)

This word is only applicable to 82541xx and 82547GI/EI Ethernet controllers that use SPI

EEPROMs. Unused bits are reserved and should be programmed to 0b. Bits 15:13 and 8:0 are

reserved (see Table 5-7).

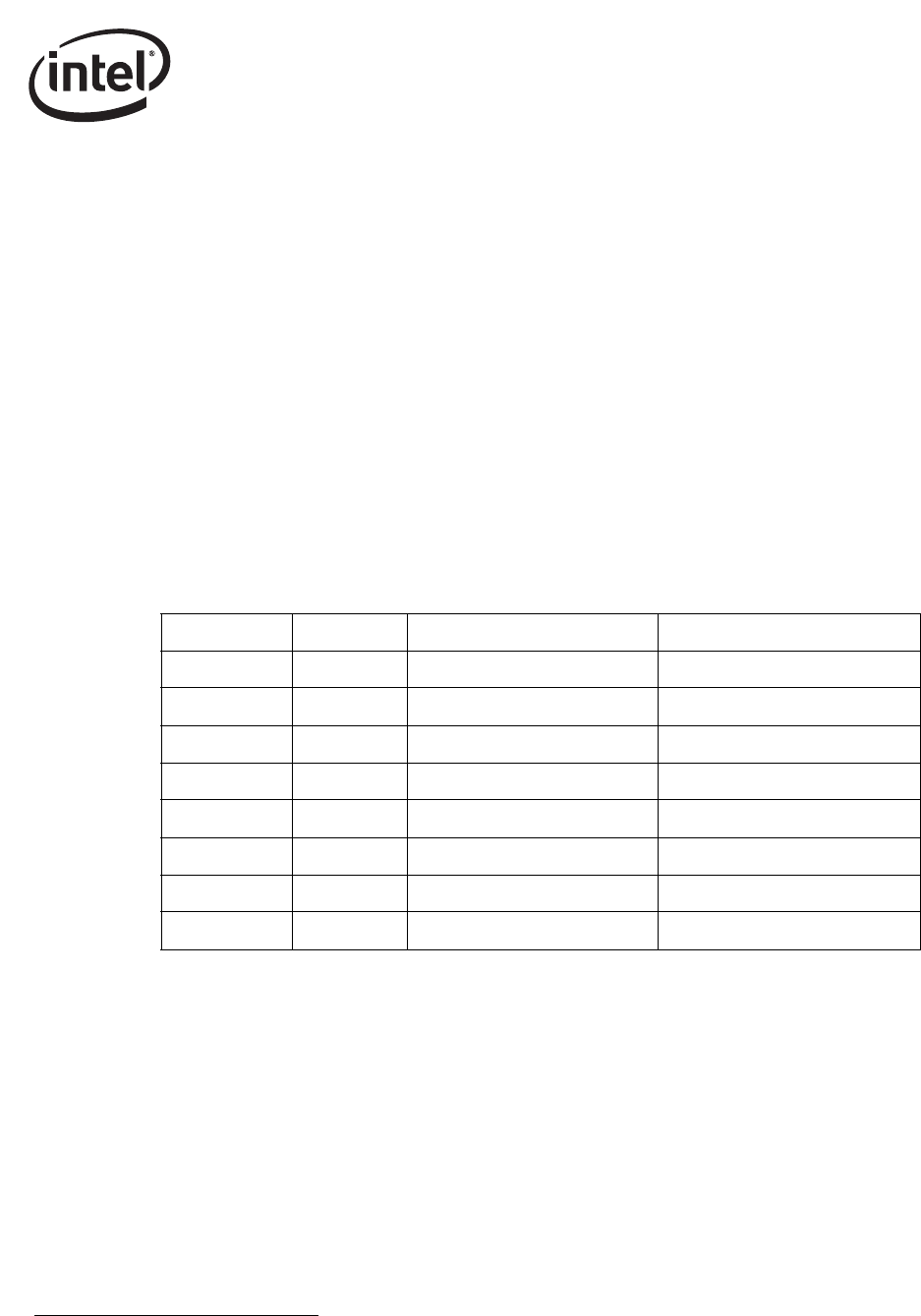

Table 5-7. SPI EEPROM Sizes

5.6.16 Common Power (Word 12h)

For all Ethernet controllers except the 82541xx and 82547GI/EI, if the signature bits are valid and

Power Management is not disabled, the value in this field is used in the PCI Power Management

Data Register when the Data_Select field of the Power Management Control/Status Register

(PMCSR) is set to 8. This setting indicates the power usage and heat dissipation of the common

logic that is shared by both functions in tenths of a watt.

5.6.17 Software Defined Pins Control (Word 10h

1

, 20h)

This field contains initial settings for the Software Defined Pins (SPD). The default value for the

upper byte (bits 15:8) is DFh; the default value for the lower byte (bits 7:0) is DEh.

Bits 12:10 Bit 9 EEPROM Size (Bits) EEPROM Size (Bytes)

000 0 1 Kb 128 Bytes

001 1 4 Kb 512 Bytes

010 1 8 Kb 1 KB

011 1 16 Kb 2 KB

100 1 32 Kb 4 KB

101 1 64 Kb 8 KB

110 1 128 Kb 16 KB

111 1 Reserved Reserved

1. Applicable to the 82546GB/EB only.