Software Developer’s Manual 289

Register Descriptions

13.4.17 Interrupt Cause Read Register

ICR (000C0H; R)

This register contains all interrupt conditions for the Ethernet controller. Each time an interrupt

causing event occurs, the corresponding interrupt bit is set in this register. A PCI interrupt is

generated each time one of the bits in this register is set, and the corresponding interrupt is enabled

through the Interrupt Mask Set/Read IMS Register (see Section 13.4.20).

All register bits are cleared upon read. As a result, reading this register implicitly acknowledges

any pending interrupt events. Writing a 1b to any bit in the register also clears that bit. Writing a 0b

to any bit has no effect on that bit.

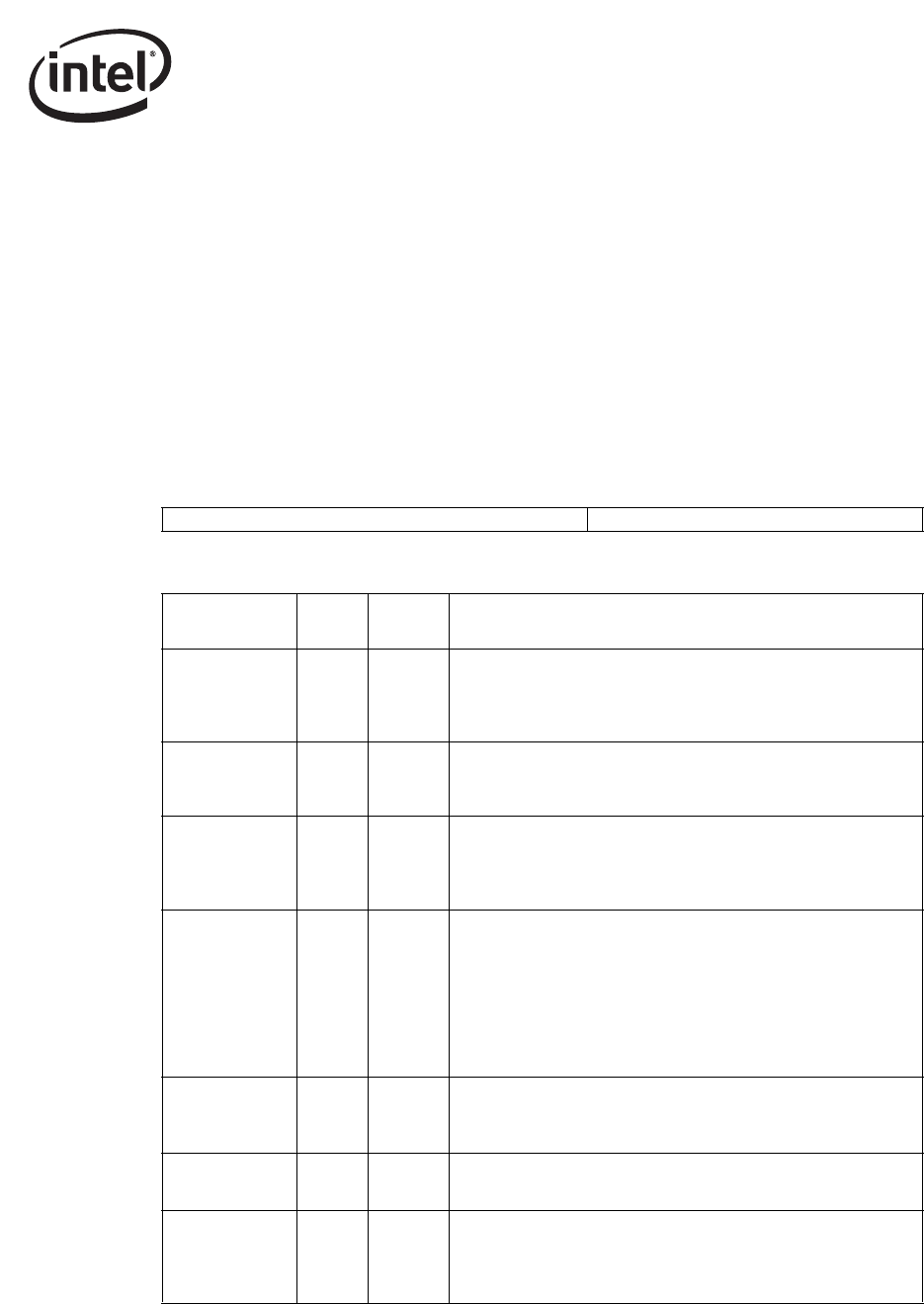

Table 13-63. ICR Register Bit Description

31 - 17 16 14 0

Reserved ICR Bits

Field Bit(s)

Initial

Value

Description

TXDW 0 0b

Transmit Descriptor Written Back

Set when hardware processes a transmit descriptor with the RS

bit set (and possibly IDE set). If using delayed interrupts (IDE set),

the interrupt occurs after the timer expires.

TXQE 1 0b

Transmit Queue Empty

Set when the last descriptor block for a transmit queue has been

used.

LSC 2 0b

Link Status Change

This bit is set each time the link status changes (either from up to

down, or from down to up). This bit is affected by the internal link

indication when configured for internal PHY mode.

RXSEQ 3 0b

Receive Sequence Error

In TBI mode/internal SerDes

1

, incoming packets with a bad

delimiter sequence set this bit. In other 802.3 implementations,

this would be classified as a framing error. A valid sequence

consists of:

idle → SOF → data → pad (opt) EOF → fill (opt) → idle.

This is a reserved bit for the 82541xx, 82547GI/EI, and 82540EP/

EM. Set to 0b.

RXDMT0 4 0b

Receive Descriptor Minimum Threshold Reached

Indicates that the minimum number of receive descriptors are

available and software should load more receive descriptors.

Reserved 5 0b

Reserved

Reads as 0b.

RXO 6 0b

Receiver Overrun

Set on receive data FIFO overrun. Could be caused either

because there are no available receive buffers or because PCI

receive bandwidth is inadequate.