282 Software Developer’s Manual

Register Descriptions

13.4.13 Transmit Configuration Word Register

1

TXCW (00178h; R/W)

This register is applicable to the TBI mode/internal SerDes mode of operation. For internal PHY

operation, program the register to 0000h. For example, clear this register in MMI mode.

This register has two meanings, depending on the state of Auto-Negotiation: one as the “AN

advertise register” defined by IEEE 802.3z, and the other as a register for software control of the

Auto-Negotiation process.

When performing hardware Auto-Negotiation, it fulfills the function defined by sub-clause

37.3.6.1.3 of IEEE 802.3z.

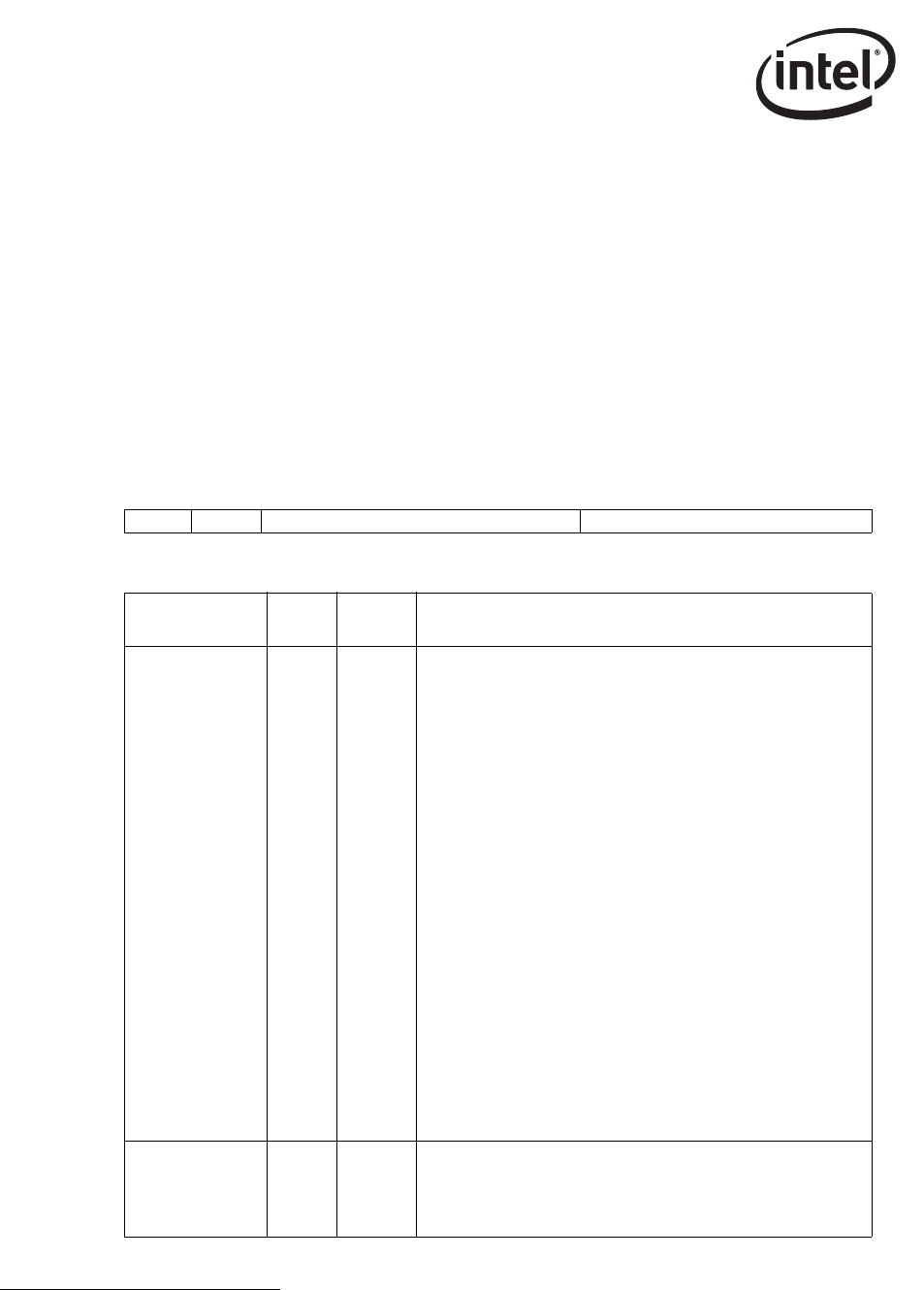

Table 13-58. TXCW Register Bit Description

1. Not applicable to the 82541xx, 82547GI/EI, or 82540EP/EM.

31 30 29 16 15 0

A Tx Reserved TxConfigWord

Field Bit(s)

Initial

Value

Description

TxConfigWord 15:0 0b

Data transmitted during Auto-Negotiation process.

When performing hardware Auto-Negotiation (TXCW.ANE is

set), the value of TxConfigWord is encoded as two 10-

bit symbols and sent as the “config_word” field for the /C/

ordered set. When the Ethernet controller performs software

Auto-Negotiation, TxConfig and TxConfigWord are used to

negotiate with the link partner. Data stored in TxConfigWord is

transmitted during the Auto-Negotiation process. Software

should not read back the contents of this field as content might

change during the software Auto-Negotiation process. In the

absence of loss of synchronization, the value read back is stable

and equal to the value written.

The mapping of the TxConfigWord is as follows:

• TxConfigWord[15] Next page request

• TxConfigWord[14] Reserved (write as 0b; ignore on read)

• TxConfigWord[13:12] Remote fault indication

• TxConfigWord[11:9] Reserved (write as 0b; ignore on read)

• TxConfigWord[8:7] Pause

• TxConfigWord[6] Half-duplex

• TxConfigWord[5] Full-duplex

• TxConfigWord[4:0] Reserved (write as 0b; ignore on read)

Bits 5,7 & 8 of TxConfigWord are loadable from the EEPROM

upon power-up, or chip reset.

Reserved 29:16 0b

Reserved

Reads as 0b.

Should be written to 0b for future compatibility.