Software Developer’s Manual 295

Register Descriptions

Software should write a 1b to the reserved bits to ensure future compatibility. Since this register

masks interrupts when 1b is written to the corresponding (defined) bits, then writing 1b to the

reserved bits ensures that the software is never called to handle an interrupt that the software is not

aware exists.

Note: For the 82547GI/EI, programmers need to first write (clear) the IMS and IMC registers due to a

Hub Link bus being occupied. This results in an interrupt de-assertion message that can’t to be sent

out. When a future interrupt assertion message is generated, two messages are re-ordered and sent

out. This signals APIC that the

82547GI/EI is in a de-asserted state when it is actually in an

asserted state, which causes a system dead lock. To avoid a system dead lock, first clear the IMS

and IMC registers by writing FFFFh and then re-assert IRQ enable.

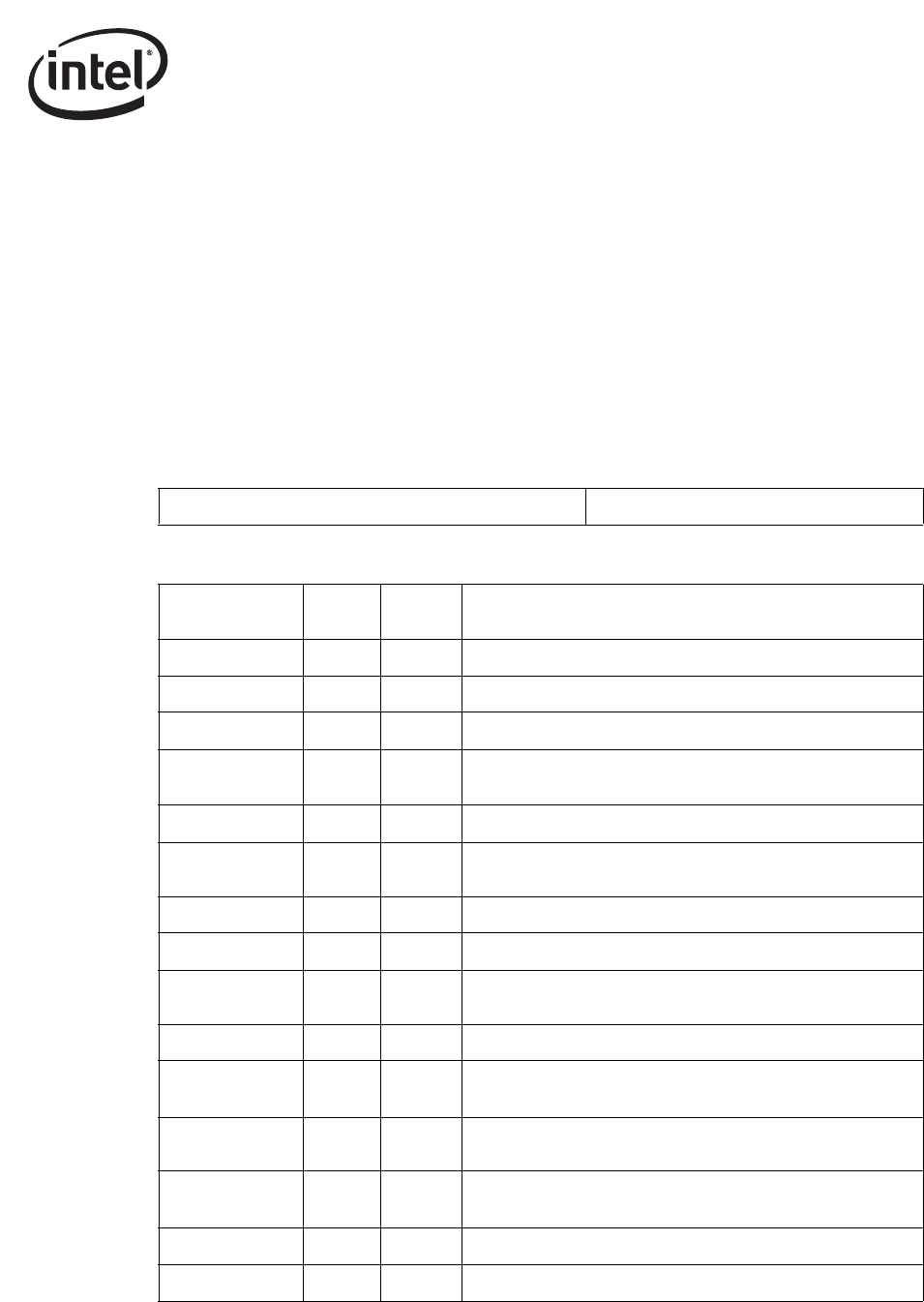

Table 13-66. IMC Register Bit Description

31 17 16 0

Reserved IMC Bits

Field Bit(s)

Initial

Value

Description

TXDW 0 X Clears mask for Transmit Descriptor Written Back.

TXQE 1 X Clears mask for Transmit Queue Empty.

LSC 2 X Clears mask for Link Status Change.

RXSEQ 3 X

Clears mask for Receive Sequence Error.

This is a reserved bit for the 82541xx and 82547GI/EI. Set to 0b.

RXDMT0 4 X Sets mask for Receive Descriptor Minimum Threshold hit.

Reserved 5 X

Reserved: Should be written with 1b to ensure future

compatibility.

RXO 6 X Clears mask for on Receiver FIFO Overrun.

RXT0 7 X Clears mask for Receiver Timer Interrupt.

Reserved 8 X

Reserved: Should be written with 1b to ensure future

compatibility.

MDAC 9 X Clears mask for MDI/O Access Complete Interrupt.

RXCFG 10 X

Clears mask for Receiving /C/ ordered sets.

This is a reserved bit for the 82541xx and 82547GI/EI. Set to 0b.

Reserved 11 X

Reserved: Should be written with 1b to ensure future

compatibility (not applicable to the 82544GC/EI).

PHYINT 12 X

Clears PHY Interrupts (not applicable to the 82544GC/EI).

This is a reserved bit for the 82541xx and 82547GI/EI. Set to 0b.

GPI 14:11 X Clears General Purpose Interrupts (82544GC/EI only).

GPI 14:13 X Clears General Purpose Interrupts.