Operating Instructions

61

For example, if bits for both ERR (128) and CC (2) are set, the power supply would send ASCII digits 1 3 0 (128 +2 =

130).

Bits remain set in the status register as long as the corresponding conditions are true.

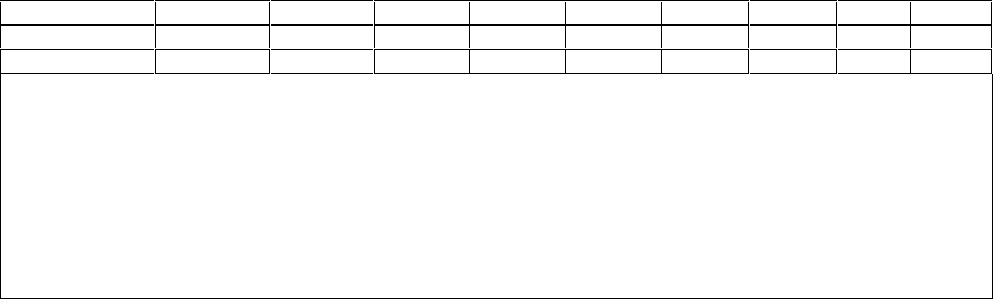

Table 3-9. Status Register

Bit Position

876543210

Bit Weight

256 128 64 32 16 8 4 2 1

Condition

RI ERR FOLD AC OT OV OR CC CV

CV Constant Voltage Mode

CC Constant Current Mode

OR Overrange

OV Overvoltage Protection Circuit Tripped

OT Overtemperature Protection Circuit Tripped

AC AC Line Dropout or Out of Range

FOLD Foldback Protection Circuit Tripped

ERR Remote Programming Error

RI Remote Inhibit (INH)

Accumulated Status Register. Reading the status register provides the controller only the state of the power supply at the

time STS? was received. A condition that lasts only momentarily may not be observed even with frequent polling of the

status register. To ensure that a temporary change can be noted by the controller, the power supply maintains an

accumulated status (astatus) register. Table 3-9 describes the astatus register as well as the status register. A bit in the astatus

register will be 1 if the corresponding bit in the status register has been 1 at any time since the astatus register was last read.

The astatus register can be read by sending:

ASTS?

and addressing the power supply to talk. The response from the power supply is in this format:

ASTS xxx

where xxx is decoded the same way as in the status register readback.

The astatus register is reset to the present value of the status register immediately after it is read by the ASTS?

query.

Mask and Fault Registers. The power supply has two additional registers, the mask register and the fault register, both of

which are arranged like the status register (Table 3-9). The mask register is maintained by the user, and is used to specify

which bits in the status register are enabled (unmasked) to set bits in the fault register. A bit is set in the fault register when

the corresponding bit in the status register changes from 0 to 1 and the corresponding bit in the mask register is 1. Whenever

any bit is set in the fault register the FAU bit is set in the serial poll register.