71

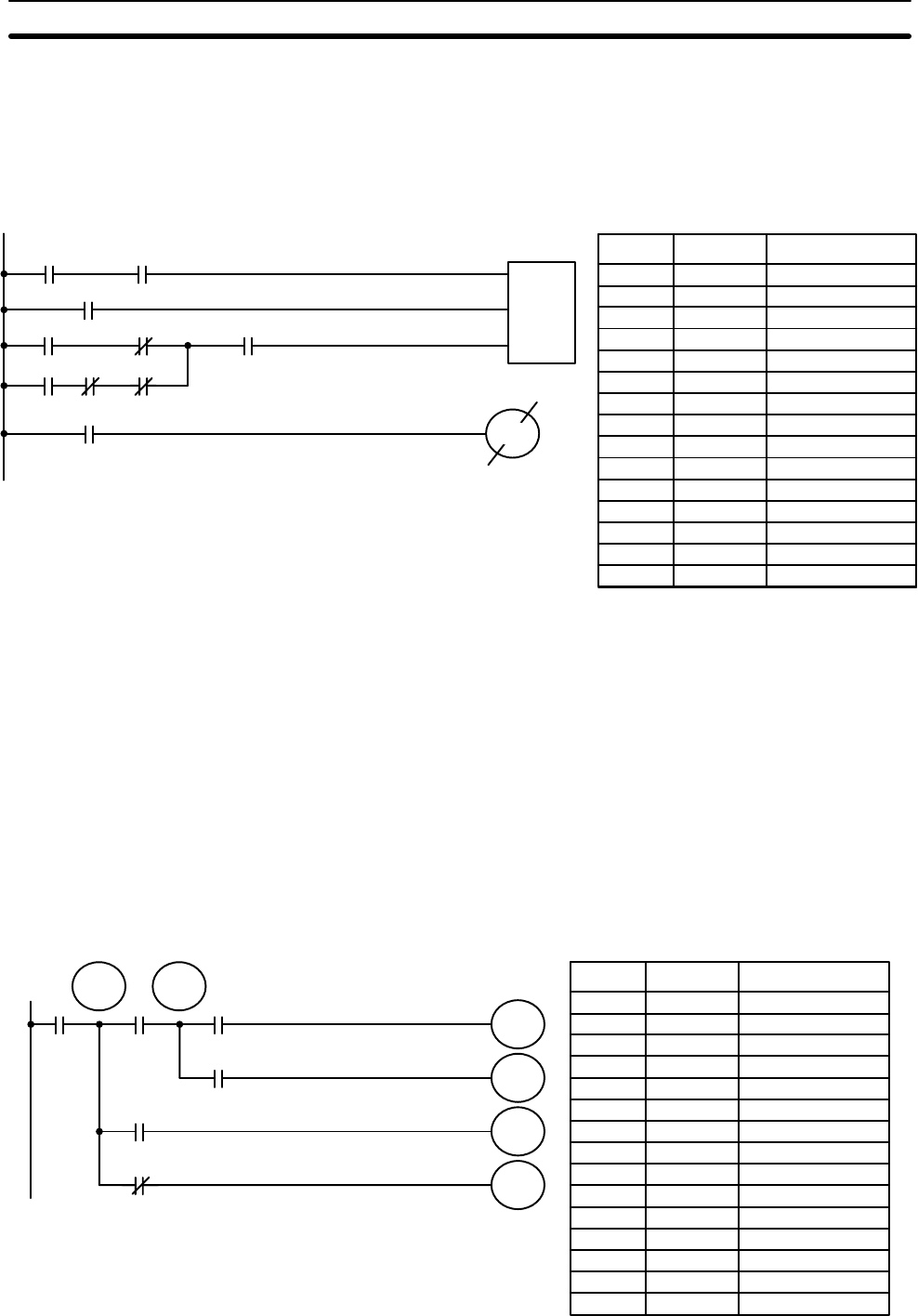

If a right-hand instruction requires multiple instruction lines, all of the lines for

the instruction are coded before the right-hand instruction. Each of the lines

for the instruction are coded starting with LD or LD NOT to form ‘logic blocks’

that are combined by the right-hand instruction. An example of this for

CNTR(12) is shown below.

I

P

R

CNTR(12)

02

#5000

0200 0203

0100

0201 0202 1501

1500

0002

HR 015

0000 0001

Address Instruction Operands

0000 LD 0000

0001 AND 0001

0002 LD 0002

0003 LD 0200

0004 AND NOT 0203

0005 LD 0201

0006 AND NOT 0202

0007 AND NOT 1501

0008 OR LD

0009 AND 1500

0010 CNTR(12)

02

# 5000

0011 LD HR 015

0012 OUT NOT 0100

TR bits in a program are used to output (OUT) the execution condition at the

branching point and then to load back (LD) the execution condition when it is

required after returning to the branch lines. Within any one instruction block,

OUT cannot be used with the same TR address. The same TR address can,

however, be used with LD as many times as required. The following example

shows an instruction block using two TR bits. TR 1 is used in LD once; TR 0,

twice.

0000 0001 0002

0003

0004

0005

0100

0101

0102

0103

TR

0

TR

1

Address Instruction Operands

0000 LD 0000

0001 OUT TR 0

0002 AND 0001

0003 OUT TR 1

0004 AND 0002

0005 OUT 0100

0006 LD TR 1

0007 AND 0003

0008 OUT 0101

0009 LD TR 0

0010 AND 0004

0011 OUT 0102

0012 LD TR 0

0013 AND NOT 0005

0014 OUT 0103

Multiple Instruction Lines

TR Bits

Data Areas, Definer Values, and Flags Section 5-4