95

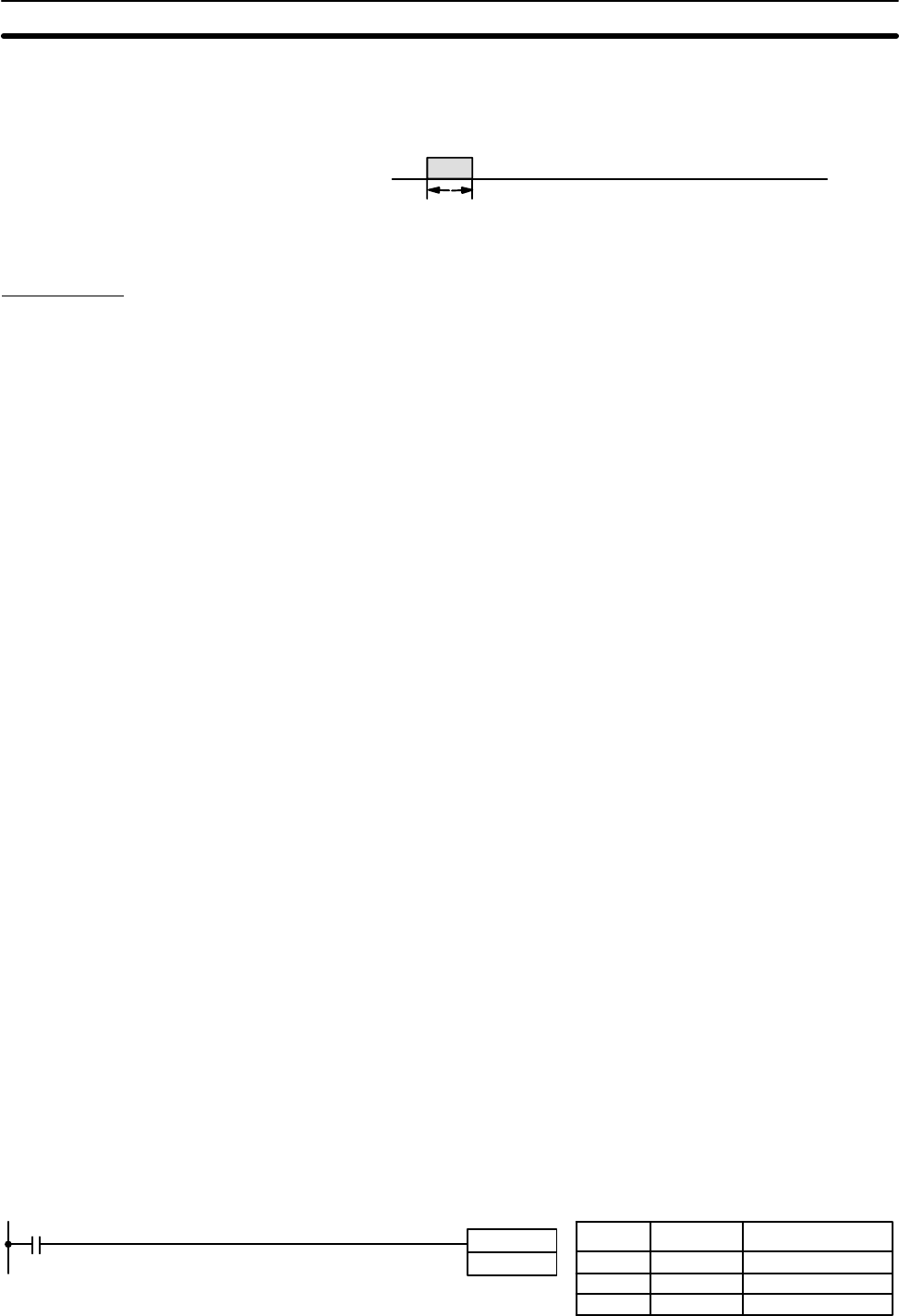

In the hard reset mode, the reset signal must have an ON time of at least

250 µs.

250 µs max.

Input

0001

Description

The high-speed counter counts the signals input from an external device con-

nected to input 0000 and, when the high-speed counter instruction is ex-

ecuted, compares the current value with a set of ranges which have been

preset in DM words 32 through 63. If the current value is within any of the

preset ranges, the corresponding bit of a specified result word is turned ON.

The bit in the result word remains ON until the current value is no longer

within the specified range.

An internal buffer is incremented whenever bit 0000 goes from OFF to ON.

When the high-speed counter instruction is executed, the value in the count-

er buffer is transferred to counter 47 which serves as the count value storage

area.

When using the high-speed counter, the following bits are reserved and can-

not be used for any other purpose:

• Input 0000 (count input)

• Input 0001 (hard reset)

• SR bit 1807 (soft reset)

• TC 47 (present count value)

• DM 32 to 63 (upper and lower limits)

Note If a power failure occurs, the count value of the high speed counter immedi-

ately before the power failure is retained.

The high-speed counter is programmed differently depending on how it is to

be reset. Two resetting modes are possible: hard-reset and soft-reset. The

hard reset is made effective or ineffective with the DIP switch in the CPU.

To use the hard reset, turn pins 7 and 8 ON. In this mode, input 0001 is the

reset input. When it is turned ON, the present value in the high-speed count-

er buffer is reset to “0000.” When the reset is ON, the count signal from input

0000 is not accepted. When programmed with the hard reset, the high-speed

counter would appear as below.

0002

HDM(61) 47

10

Address Instruction Operands

0000 LD 0002

0001 HDM(61) 47

10

General

Hard Reset

Timer and Counter Instructions Section 5-11