40

There are two means of programming branching programs to preserve the

execution conditions. One is to use TR bits; the other, to use interlocks

(IL(02)/ILC(03)).

The TR area provides eight bits, TR 0 through TR 7, that can be used to tem-

porarily preserve execution conditions. If a TR bit is used as the operand of

the OUTPUT instruction placed at a branching point, the current execution

condition will be stored at the designated TR bit. Storing execution conditions

is a special application of the OUTPUT instruction. When returning to the

branching point, the same TR bit is then used as the operand of the LOAD

instruction to restore the execution condition that existed when the branching

point was first reached in program execution.

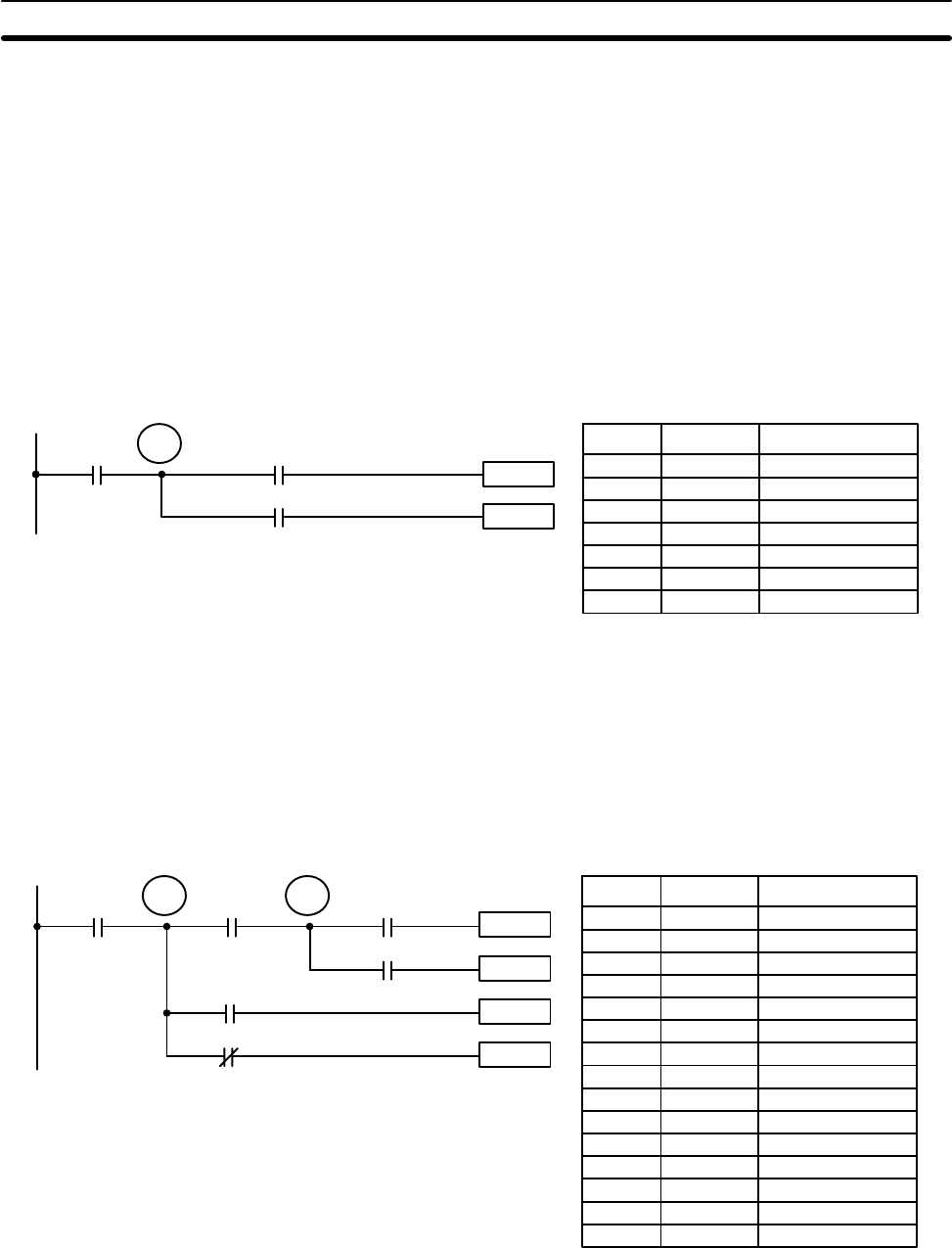

The above diagram B can be written as shown below to ensure correct exe-

cution.

Instruction 1

0002

0000

Instruction 2

Diagram B: Corrected Using a TR bit

0001

TR 0

Address Instruction Operands

0000 LD 0000

0001 OUT TR 0

0002 AND 0001

0003 Instruction 1

0004 LD TR 0

0005 AND 0002

0006 Instruction 2

In terms of actual instructions the above diagram would be as follows: The

status of 0000 is loaded (a LOAD instruction) to establish the initial execution

condition. This execution condition is then output using an OUTPUT instruc-

tion to TR 0 to store the execution condition at the branching point. The exe-

cution condition is then ANDed with the status of 0001 and instruction 1 is

executed accordingly. The execution condition that was stored at the branch-

ing point is then loaded back in (a LOAD instruction with TR 0 as the oper-

and) and instruction 2 is executed accordingly.

The following example shows an application using two TR bits.

Instruction 1

0003

0000 0002

TR 1

0005

TR 0

0001

0004

Instruction 2

Instruction 3

Instruction 4

Address Instruction Operands

0000 LD 0000

0001 OUT TR 0

0002 AND 0001

0003 OUT TR 1

0004 AND 0002

0005 OUT 0500

0006 LD TR 1

0007 AND 0003

0008 OUT 0501

0009 LD TR 0

0010 AND 0004

0011 OUT 0502

0012 LD TR 0

0013 AND NOT 0005

0014 OUT 0503

In this example, TR 0 and TR 1 are used to store the execution conditions at

the branching points. After executing instruction 1, the execution condition

stored in TR 1 is loaded for an AND with the status 0003. The execution con-

dition stored in TR 0 is loaded twice, the first time for an AND with the status

of 0004 and the second time for an AND with the inverse of the status of

0005.

TR Bits

The Ladder Diagram Section 4-3