42

The problem of storing execution conditions at branching points can also be

handled by using the INTERLOCK (IL(02)) and INTERLOCK CLEAR

(ILC(03)) instructions. The branching point and all the conditions leading to it

are placed on a separate line followed by all of the lines from the branching

point. Each branch line is thus established as an new instruction line, with the

first condition on each branch line corresponding to a LOAD or LOAD NOT

instruction. If the execution condition for the INTERLOCK instruction is OFF,

all instructions on the right side of the branch lines leading from the branch-

ing point receive an OFF execution condition through the first INTERLOCK

CLEAR instruction. The effect that this has on particular instructions is de-

scribed in

5-7 INTERLOCK and INTERLOCK CLEAR - IL(02) and ILC(03)

.

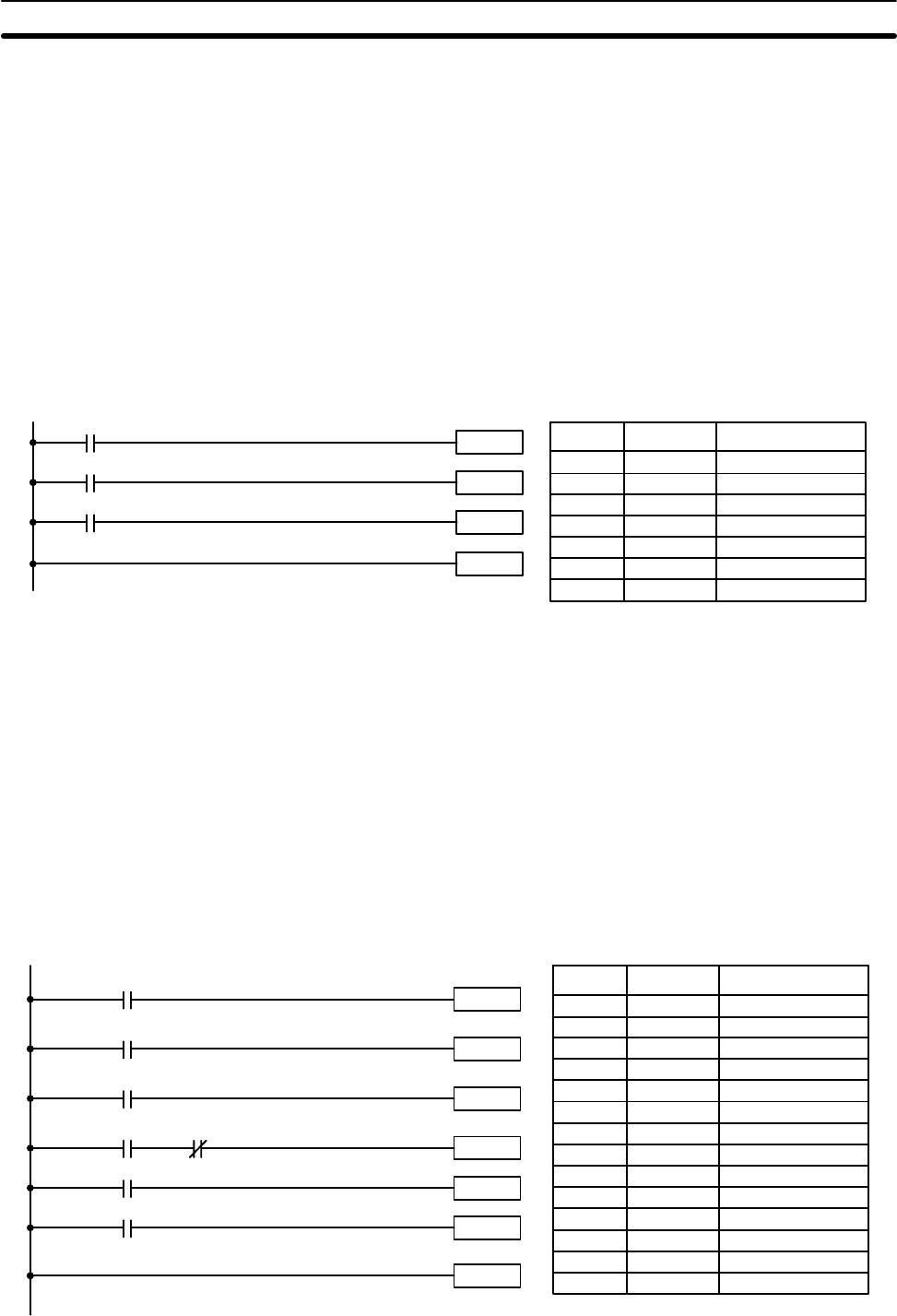

Diagram B from the initial example can also be corrected with an interlock.

As shown below, this requires two more instruction lines for the interlock in-

structions.

Instruction 1

0002

0000

Instruction 2

Diagram B: Corrected with an Interlock

0001

ILC(03)

IL(02)

Address Instruction Operands

0000 LD 0000

0001 IL(02) ---

0002 LD 0001

0003 Instruction 1

0004 LD 0002

0005 Instruction 2

0006 ILC(03) ---

If 0000 is ON in the revised version of diagram B, above, the status of 0001

and that of 0002 would determine the execution conditions for instructions 1

and 2, respectively, on independent instruction lines. Because here 0000 is

ON, this would produce the same results as ANDing the status of each of

these bits, as would occur if the interlock was not used, i.e., the INTERLOCK

and INTERLOCK CLEAR instructions would not affect execution. If 0000 is

OFF, the INTERLOCK instruction would produce an OFF execution condition

for instructions 1 and 2 and then execution would continue with the instruc-

tion line following the INTERLOCK CLEAR instruction.

As shown in the following diagram, more than one INTERLOCK instruction

can be used within one instruction block; each is effective through the next

INTERLOCK CLEAR instruction.

Instruction 1

0000

Instruction 2

0001

ILC(03)

IL(02)

0004

Instruction 3

Instruction 4

0006

0005

0003

0002

IL(02)

Address Instruction Operands

0000 LD 0000

0001 IL(02) ---

0002 LD 0001

0003 Instruction 1

0004 LD 0002

0005 IL(02) ---

0006 LD 0003

0007 AND NOT 0004

0008 Instruction 2

0009 LD 0005

0010 Instruction 3

0011 LD 0006

0012 Instruction 4

0013 ILC(03) ---

Interlocks

The Ladder Diagram Section 4-3