336 Software Developer’s Manual

Register Descriptions

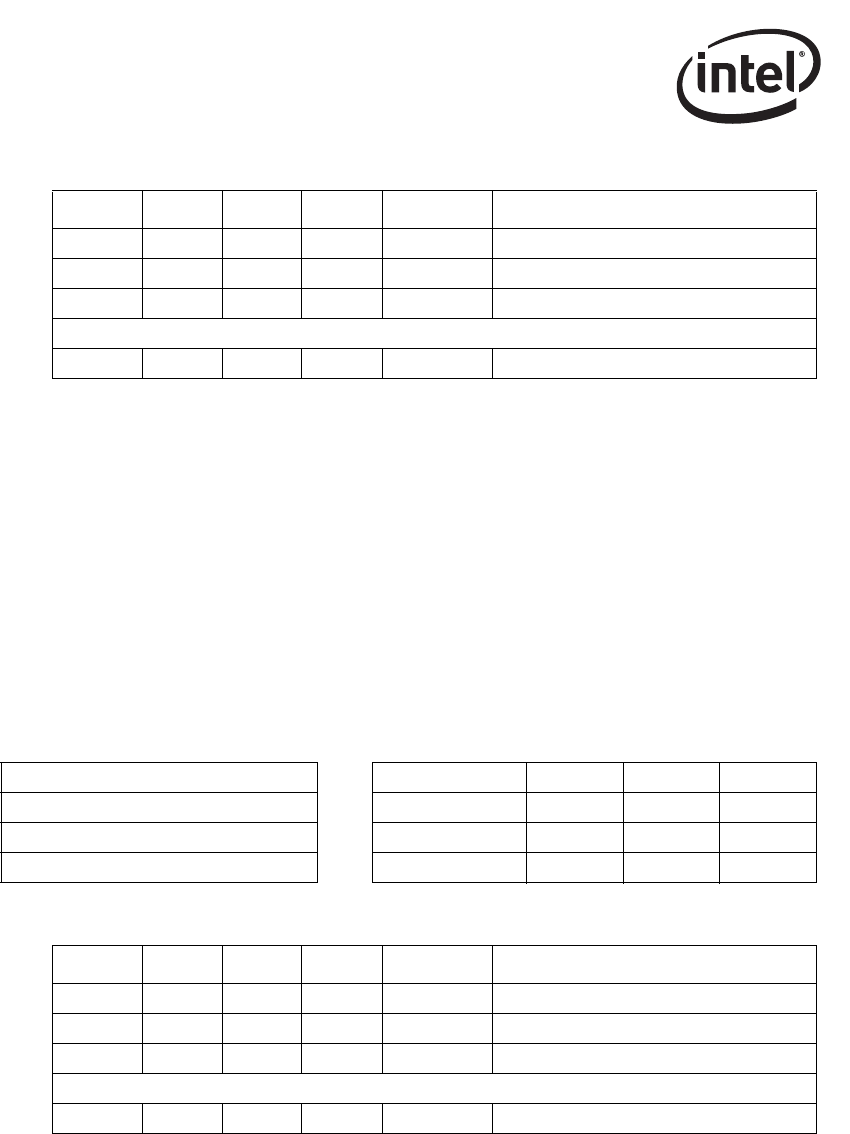

13.6.11 Flexible Filter Value Table

FFVT (09800h - 09BF8h; R/W)

The Flexible Filter Value and Table is used to store the one value for each byte location in a packet

for each flexible filter. If the corresponding mask bit is set to 1b, the Flexible Filter compares the

incoming data byte to the values stored in this table.

Before writing to the Flexible Filter Value Table the driver must first disable the flexible filters by

writing 0b’s to the Flexible Filter Enable bits of the Wakeup Filter Control Register

(WUFC.FLXn).

13.7 Statistics Registers

All statistics registers are implemented as 32-bit registers. 64-bit accesses to these registers must

have the upper byte enables de-asserted. 32-bit registers with addresses not on a quadword

boundary cannot be accessed through a 64-bit access.

Registers that count octets make up 64-bit registers.

Field Dword # Address Bit(s) Initial Value Description

MASK0 0 9000h 15:0 X Mask for Filter [3:0] for Byte 0

MASK1 2 9008h 15:0 X Mask for Filter [3:0] for Byte 2

MASK2 4 9010h 15:0 X Mask for Filter [3:0] for Byte 3

...

MASK127 254 93F8h 15:0 X Mask for Filter [3:0] for Byte 127

31 0 31 24 23 16 15 8 7 0

Reserved Byte0: Value3 Value2 Value1 Value0

Reserved Byte1: Value3 Value2 Value1 Value0

Reserved Byte2: Value3 Value2 Value1 Value0

Reserved Byte127: Value3 Value2 Value1 Value0

Field Dword # Address Bit(s) Initial Value Description

MASK0 0 9800h 15:0 X Mask for Filter [3:0] for Byte 0

MASK1 2 9808h 15:0 X Mask for Filter [3:0] for Byte 2

MASK2 4 9810h 15:0 X Mask for Filter [3:0] for Byte 3

...

MASK127 254 9BF8h 15:0 X Mask for Filter [3:0] for Byte 127