Software Developer’s Manual 185

PHY Functionality and Features

11.1.4 Status

Once the PHY completes auto-negotiation, it updates the various statuses in the PHY Status

Register, Link Partner Ability Register (Base Page), Auto-Negotiation Expansion Register, and

1000BASE-T Status Register. For 1000BASE-T operation, the Auto-Negotiation Expansion

Register and the Link Partner Ability Register (Base Page) are updated. Speed, duplex, page

received, and Auto-Negotiation completion statuses are also available in the PHY Specific Status

Register (PSTATUS) and the PHY Interrupt Status Register (PINTS).

For fiber, the CTRL.STATUS register will reflect link status.

Assuming normal MAC configuration, the MAC status register STATUS reports bits SPEED, FD

(duplex/half indication), and LU (link up status) shortly after the PHY (or MAC, for fiber)

completes auto-negotiation.

11.2 MDI/MDI-X Crossover (copper only)

The Ethernet controller PHY automatically determines whether or not it needs to cross over

between pairs as shown in the following table so that an external crossover cable is not required. If

the PHY interoperates with a device that cannot automatically correct for crossover, the Ethernet

controller PHY makes the necessary adjustment prior to commencing Auto-Negotiation. If the

PHY operates with a device that implements MDI/MDI-X crossover, a random algorithm as

described in IEEE 802.3 clause 40.4.4 determines which device performs the crossover.

When the Ethernet controller PHY interoperates with legacy 10BASE-T devices that do not

implement Auto-Negotiation, the PHY follows the same algorithm as described above since link

pulses are present. However, when interoperating with legacy 100BASE-TX devices that do not

implement Auto-Negotiation (link pulses are not present), the Ethernet controller PHY uses signal-

detection to determine whether to crossover.

Auto MDI/MDI-X crossover is the default hardware configuration, but can be disabled via the

PHY Specific Control Register bits 6:5 (PSCON).

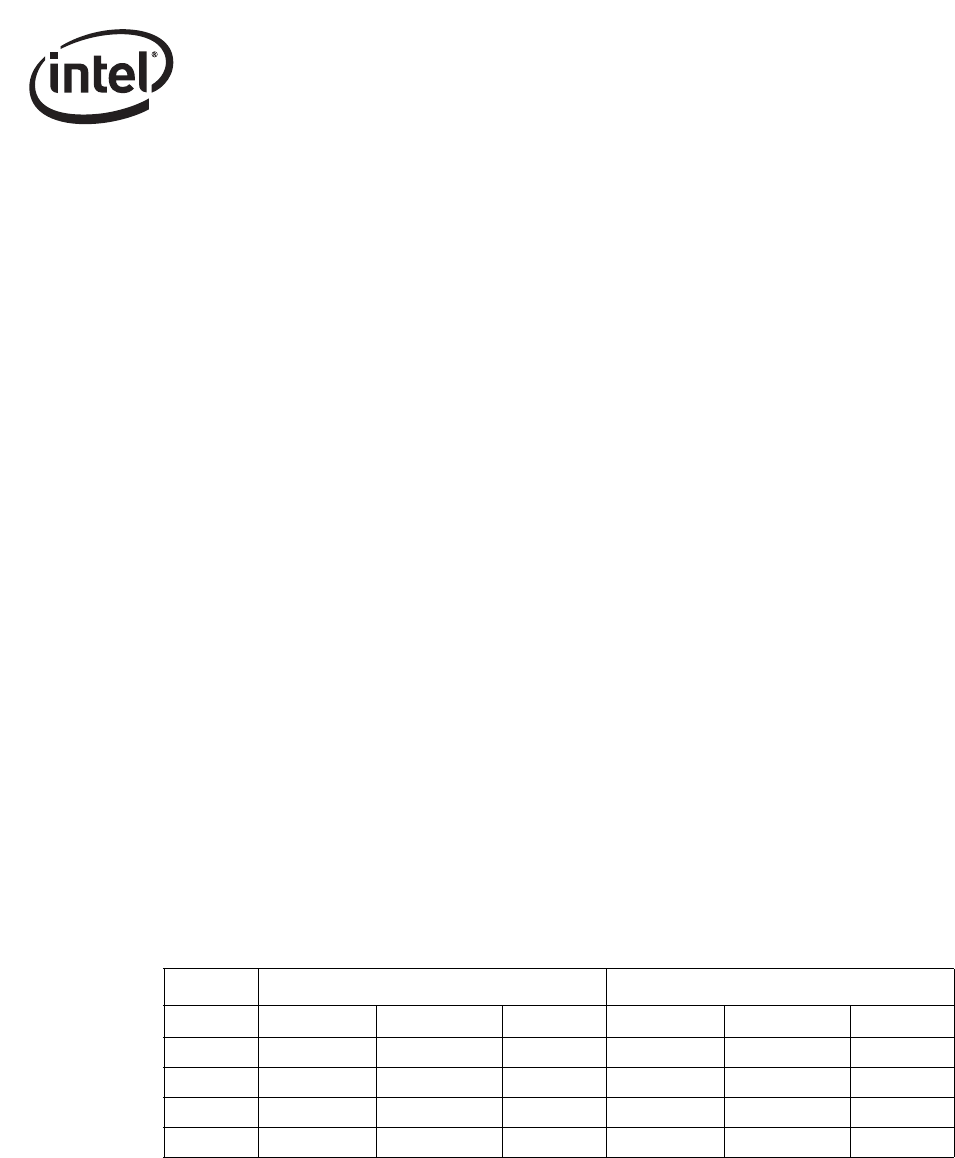

The pin mapping in MDI/MDI-X modes are as follows:

Pin MDI MDIX

1000BASE-T 100BASE-TX 10BASE-T 1000BASE-T 100BASE-TX 10BASE-T

MDI[0]+/- BI_DA +/- TX +/- TX +/- BI_DB +/- RX +/- RX +/-

MDI[1]+/- BI_DB +/- RX +/- RX +/- BI_DA +/- TX +/- TX +/-

MDI[2]+/- BI_DC +/- unused unused BI_DD +/- unused unused

MDI[3]+/- BI_DD +/- unused unused BI_DC +/- unused unused