Software Developer’s Manual 259

Register Descriptions

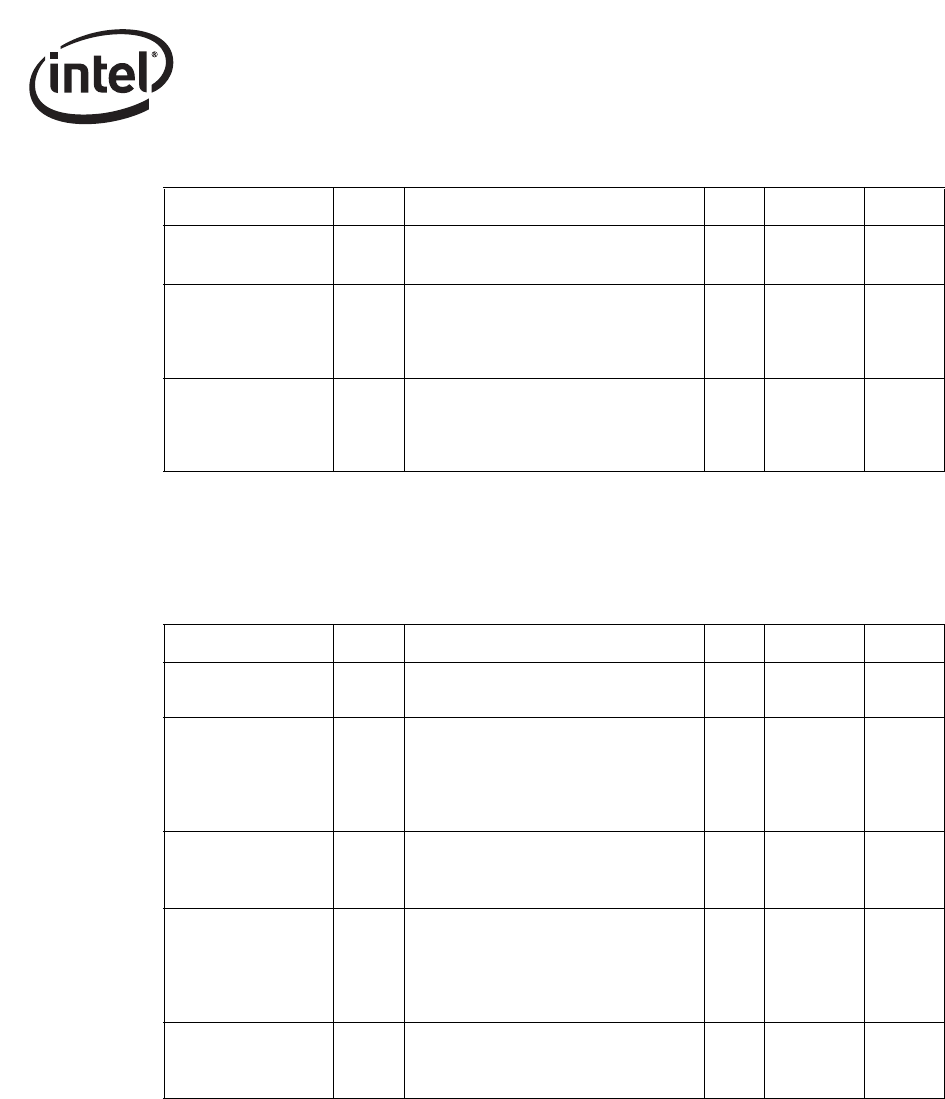

13.4.7.1.12 Extended PHY Status Register

EPSTATUS (15d; R)

NOTES:

1. 1000BASE-X Half Duplex only applicable to the 82544GC/EI.

2. Bit 12 = bit 13 = 1b if MODE[3:0] does not = 001xb or 0111b.

3. Bit 14 = bit 15 = 1b if MODE[3:0] = 001xb or 0111b.

Local Receiver Status 13

1b = Local Receiver OK.

0b = Local Receiver Not OK.

RO 0b 0b

MASTER/SLAVE

Configuration

Resolution

14

1b = Local PHY configuration resolved

to MASTER.

0b = Local PHY configuration resolved

to SLAVE.

RO 0b 0b

MASTER/SLAVE

Configuration Fault

15

1b = MASTER/SLAVE configuration

fault detected.

0b = No MASTER/SLAVE configuration

fault detected.

RO,

LH,

SC

0b 0b

Table 14-29. 1000BASE-T Status Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Table 13-30. Extended PHY Status Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Reserved 11:0

Reserved. Should be set to

000000000000b.

RO 000h 000h

1000BASE-T Half

Duplex

12

1b = 1000BASE-T half duplex capable.

0b = not 1000BASE-T half duplex

capable.

Note: 1000Mb-Half duplex is NOT

supported.

RO 1b

1

1. MODE[3:0] 82544GC/EI only.

1b

1

1000BASE-T Full

Duplex

13

1b = 1000BASE-T full duplex capable.

0b = Not 1000BASE-T full duplex

capable.

RO 1b

1

1b

1

1000BASE-X Half

Duplex

14

1b =1000BASE-X half duplex capable.

0b = Not 1000BASE-X half duplex

capable.

Note: 1000Mb-Half Duplex is NOT

supported.

RO 0b

1

0b

1

1000BASE-X Full

Duplex

15

1b =1000BASE-X full duplex capable.

0b = Not 1000BASE-X full duplex

capable.

RO 0b

1

0b

1