Software Developer’s Manual 307

Register Descriptions

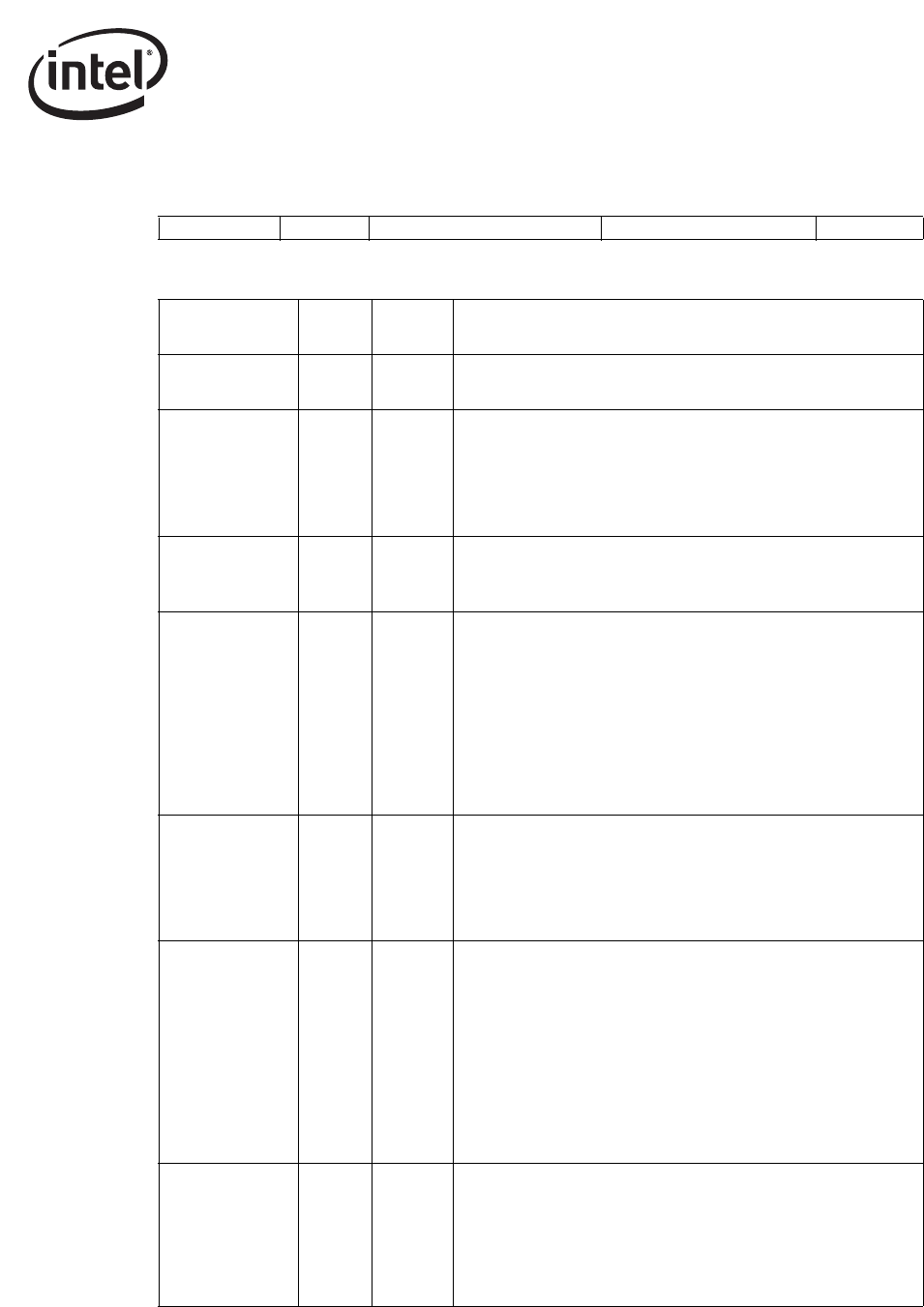

Table 13-76. TCTL Register Bit Description

31 26 25 22 21 12 11 4 3 0

Reserved CNTL Bits COLD CT CNTL Bits

Field Bit(s)

Initial

Value

Description

Reserved 0 0b

Reserved

Write as 0b for future compatibility.

EN 1 0b

Transmit Enable

The transmitter is enabled when this bit is set to 1b. Writing 0b to

this bit stops transmission after any in progress packets are sent.

Data remains in the transmit FIFO until the device is re-enabled.

Software should combine this operation with reset if the packets in

the TX FIFO should be flushed.

Reserved 2 0b

Reserved

Reads as 0b.

Should be written to 0b for future compatibility.

PSP 3 0b

Pad Short Packets

0b = Do not pad.

1b = Pad short packets.

Padding makes the packet 64 bytes long. The padding content is

data.

When the Pad Short Packet feature is disabled, the minimum

packet size the Ethernet controller can transfer to the host is 32

bytes long.

This feature is not the same as Minimum Collision Distance

(TCTL.COLD).

CT 11:4 0b

Collision Threshold

This determines the number of attempts at re-transmission prior to

giving up on the packet. The Ethernet back–off algorithm is

implemented and clamps to the maximum value after 16 retries. It

only has meaning in half-duplex operation. Recommended value –

0Fh.

COLD 21:12 0b

Collision Distance

Specifies the minimum number of byte times that must elapse for

proper CSMA/CD operation. Packets are padded with special

symbols, not valid data bytes. Hardware checks this value and

padded packets even in full-duplex operation.

Recommended value:

Half-Duplex – 512-byte time (200h)

Full-Duplex – 64-byte time (40h)

Note: 10/100 half-duplex - 64 - 68 (40h to 44h) byte times for the

82541xx and 82547GI/EI only.

SWXOFF 22 0b

Software XOFF Transmission

When set to 1b, the Ethernet controller schedules the transmission

of an XOFF (PAUSE) frame using the current value of the PAUSE

timer (FCTTV.TTV). This bit self-clears upon transmission of the

XOFF frame. This bit is valid only in Full-Duplex mode of

operation. Software should not set this bit while the Ethernet

controller is configured for half-duplex operation.