262 Software Developer’s Manual

Register Descriptions

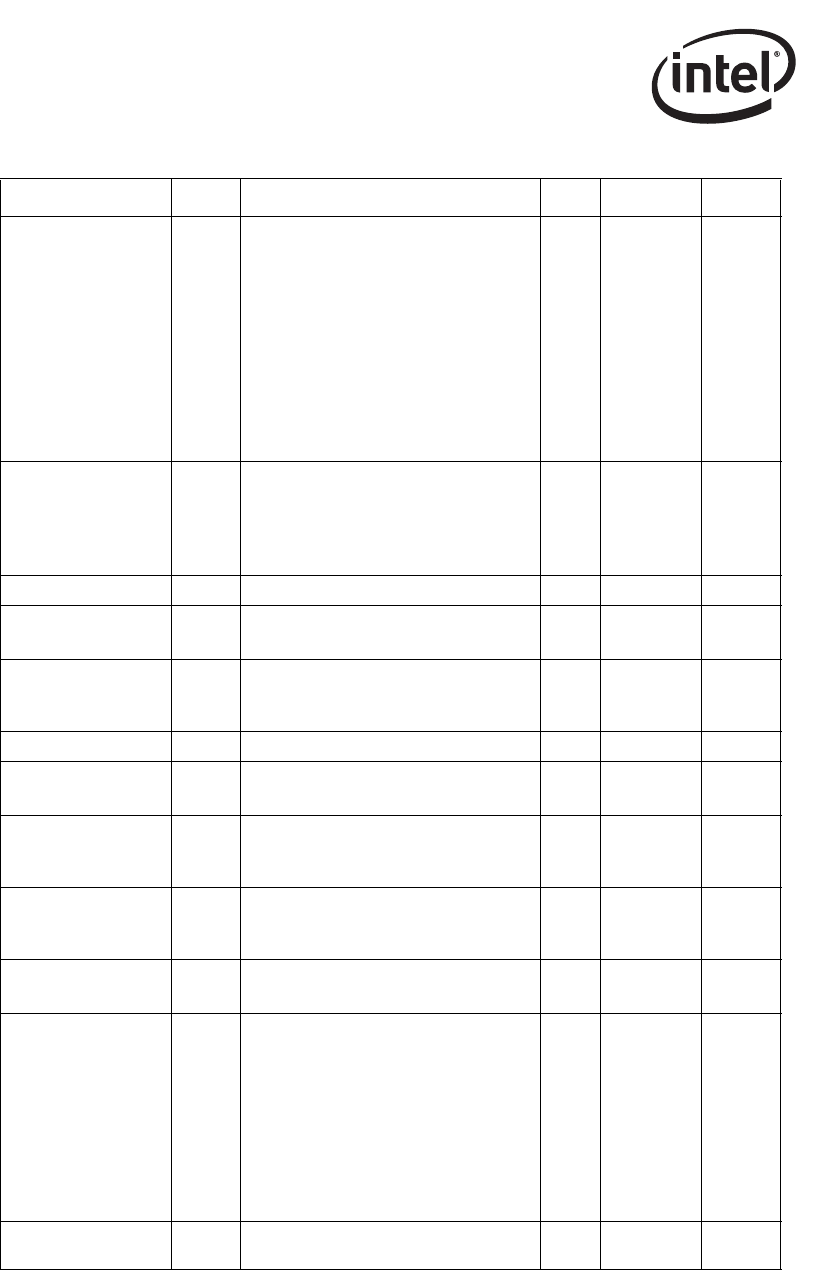

Auto MDIX Parallel

Detect Bypass

4

Auto_MDIX Parallel Detect Bypass.

Bypasses the fix to IEEE auto-MDIX

algorithm for the case where the PHY is

in forced-speed mode and the link

partner is auto-negotiating.

1b = Strict 802.3 Auto-MDIX algorithm.

0b = Auto-MDIX algorithm handles

Auto-Negotiation disabled modes. This

is accomplished by lengthening the

auto-MDIX switch timer before

attempting to swap pairs on the first time

out.

R/W 0b 0b

PRE_EN 5

Preamble Enable

0b = Set RX_DV high coincident with

SFD.

1b = Set RX_DV high and RXD =

preamble (after CRS is asserted).

R/W 1b 1b

Reserved 6 Write to 0b for normal operation. R/W 0b 0b

Smart Speed 7

1b = Smart Speed selection enabled.

0b = Smart Speed selection disabled.

R/W 0b 0b

1

TP Loopback

(10BASE-T)

8

1b = Disable TP loopback during half-

duplex operation.

0b = Normal operation.

R/W 1b 1b

Reserved 9 Write to 0b for normal operation. R/W 0b 0b

Jabber (10BASE-T) 10

1b = Disable jabber.

0b = Enable jabber.

R/W 0b 0b

Bypass 4B5B

(100BASE-TX)

11

1b = Bypass4B5B encoder and

decoder.

0b = Normal operation.

R/W 0b 0b

Bypass Scramble

(100BASE-TX)

12

1b = Bypass scrambler and

descrambler.

0b = Normal operation.

R/W 0b 0b

Transmit Disable 13

1b = Disable twisted-pair transmitter.

0b = Normal operation.

R/W 0b 0b

Link Disable 14

1b = Force link pass

0b = Normal operation

For 10BASE-T, this bit forces the link

signals to be active. In 100BASE-T

mode, setting this bit should force the

Link Monitor into it’s LINKGOOD state.

For Gigabit operation, this merely

bypasses Auto-Negotiation—the link

signals still correctly indicate the

appropriate status.

R/W 0b 0b

Reserved 16:15

Always read as 0b. Write 0b for normal

operation.

R/W 0b 0b

1. The default for this bit is determined by EEPROM bit SSPEED.

Table 13-32. PHY Port Configuration Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst