Software Developer’s Manual 253

Register Descriptions

82541xx and 82547GI/EI Only:

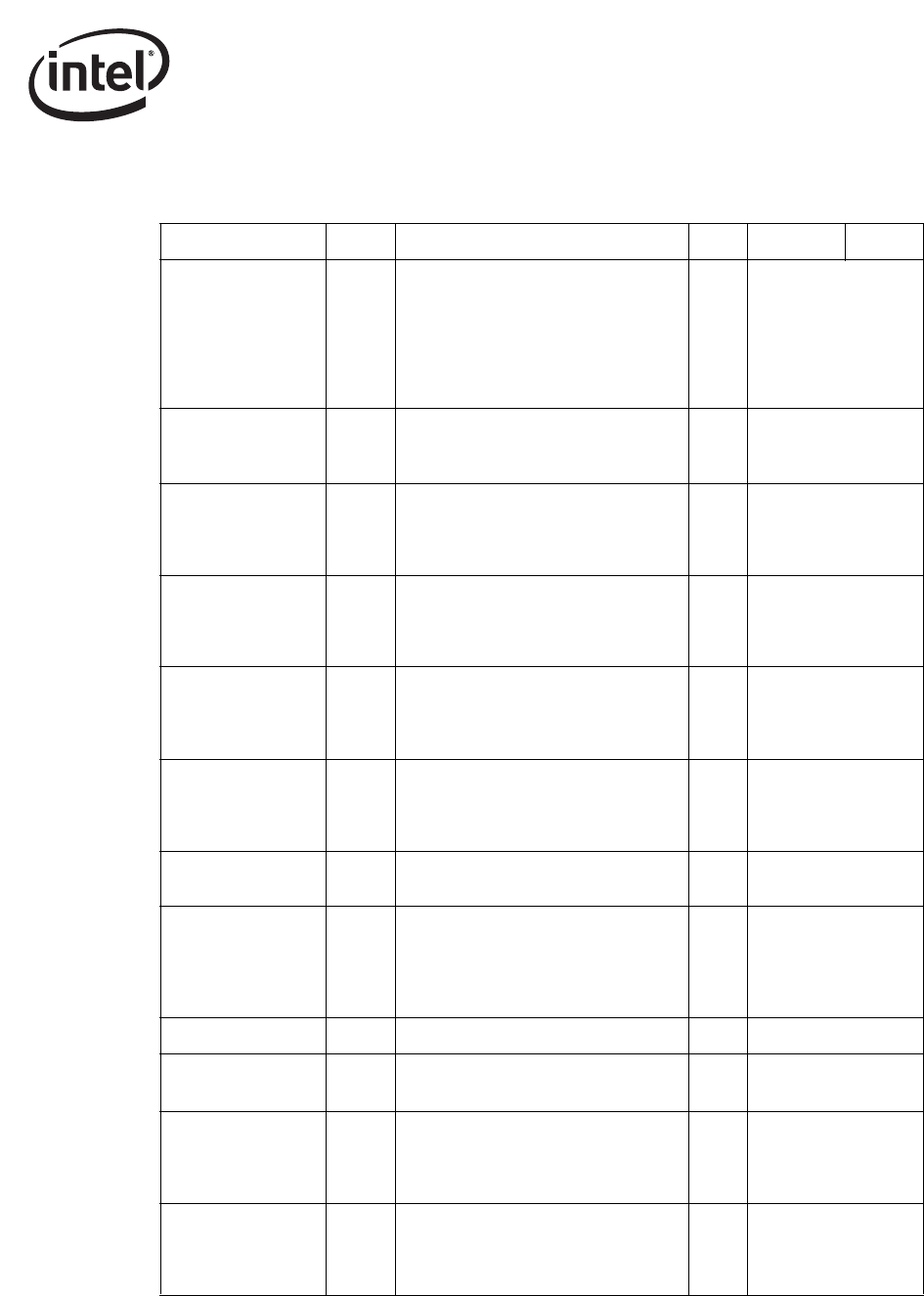

Table 13-24. PHY Link Page Ability Bit Description

1

1. PHY register 8d stores the Auto-Negotiation Link Partner Received Next Pages. PHY register 5d is not used to store Next

Pages. It contains the information from the last Base Page correctly received.

Field Bit(s) Description Mode HW Rst SW Rst

Selector Field [4:0] 4:0

<00001> = IEEE 802.3

Other combinations are reserved.

Unspecified or reserved combinations

shall not be transmitted.

If field does not match PHY Register 4,

bits 4:0, the AN process does not

complete and no HCD is selected.

RO N/A

10BASE-T 5

1b = Link Partner is 10BASE-T capable.

0b = Link Partner is not 10BASE-T

capable.

RO N/A

10BASE-T Full

Duplex

6

1b = Link Partner is 10BASE-T full

duplex capable.

0b = Link Partner is not 10BASE-T full

duplex capable.

RO N/A

100BASE-TX 7

1b = Link Partner is 100BASE-TX

capable.

0b = Link Partner is not 100BASE-TX

capable.

RO N/A

100BASE-TX Full

Duplex

8

1b = Link Partner is 100BASE-TX full

duplex capable.

0b = Link Partner is not 100BASE-TX

full duplex capable.

RO N/A

100BASE-T4 9

1b = Link Partner is 100BASE-T4

capable.

0b = Link Partner is not 100BASE-T4

capable.

RO N/A

LP Pause 10

Link Partner uses Pause Operation as

defined in 802.3x.

RO N/A

LP ASM_DIR 11

Asymmetric Pause Direction Bit

1b = Link Partner is capable of

asymmetric pause.

0b = Link Partner is not capable of

asymmetric pause.

RO N/A

Reserved 12 Reserved. Should be set to 0b. RO 0b

Remote Fault 13

1b = Remote fault.

0b = No remote fault.

RO N/A

Acknowledge 14

1b = Link Partner has received Link

Code Word from the PHY.

0b = Link Partner has not received Link

Code Word from the PHY.

RO N/A

Next Page 15

1b = Link Partner has ability to send

multiple pages.

0b = Link Partner has no ability to send

multiple pages.

RO N/A