Software Developer’s Manual 139

Power Management

6.3.3.4 Power Management Control / Status Register - (PMCSR)

2 Bytes Offset = 4 (RO)

This register is used to control and monitor power management events in the Ethernet controller. If

auxiliary power is present, as indicated by AUX_POWER = 1b, a PCI reset does not clear

PME_En and PME_Status.

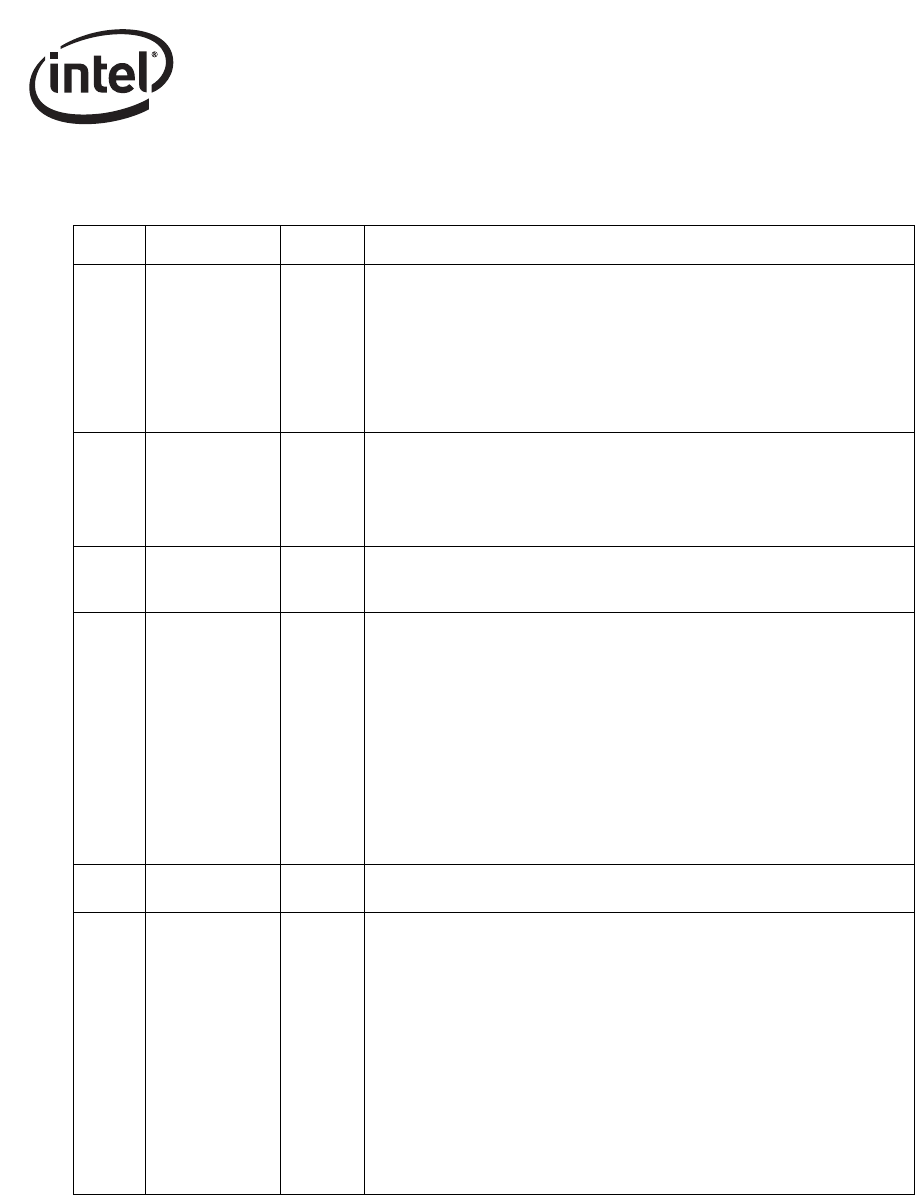

Bits Default R/W Description

15

0b (see

description)

Read/

Write 1b

to clear

PME_Status – This bit is set when the function would normally assert the

PME# signal independent of the state of the PME_En bit. The Ethernet

controller returns a value of 1b for this bit if a Wakeup condition has been

detected.

Writing a 1b clears this bit and deasserts PME#

a

.

If the AUX_POWER input is 1b, the PME_Status field is only reset by

LAN_PWR_GOOD. If AUX_POWER is 0b, PME_Status is also reset on the

deassertion (rising edge) of RST#.

a. Not applicable to the 82541ER.

14:13

00b

01b if

Manageability is

enabled

(see description)

Read

Only

Data_Scale - This 2- bit read-only field indicates the scaling factor to be

used when interpreting the value of the Data register. This field outputs 01b

(to indicate units of 0.1 watt) when Manageability is enabled in the

EEPROM and the Data_Select field is set to 0, 3, 4, or 7, and 00b

otherwise.

12:09 0000b

Read/

Write

Data_Select - This 4-bit field is used to select which data is to be reported

through the Data register and Data_Scale field. These bits are only writable

when Power Management is enabled via EEPROM.

08

0b on Power-On

reset

Read/

Write

PME_En – If Power Management is not disabled in the EEPROM, writing a

1b to this register enables Wakeup and causes the Ethernet controller to

assert PME# when it receives a Wakeup event enabled in the Wakeup Filter

Control Register (WUFC).

Note: This bit cannot be set for the 82541ER.

If Power Management is disabled in the EEPROM, writing a 1b to this bit

has no affect, and does not set the bit to 1b.

If the AUX_POWER input is 1b, the PME_En field is only reset by

LAN_PWR_GOOD. If AUX_POWER is 0b, it is also reset on the

deassertion (rising edge) of RST#.

Note: If APM Wakeup is enabled, the PME# pin can be asserted even if

PME_En is 0b. See Section 6.4.1 for details.

07:02 000000b

Read

Only

Reserved - The Ethernet controller returns a value of 000000b for this field.

01:00 00b

Read/

Write

PowerState - This 2-bit field is used both to determine the current power

state of a function and to set the function into a new power state. The

definition of the field values is as follows:

00b - D0

01b - D1 (ignored if written with this value)

10b - D2 (ignored if written with this value)

11b - D3

If software attempts to write an unsupported state to this field, 00b or 10b, or

if Power Management is disabled in the EEPROM, then the Ethernet

controller completes the write operation normally on the bus, however the

data is discarded and no state change occurs.

These bits are cleared and the power state is returned to D0 after the trailing

edge of RST#.