Software Developer’s Manual 137

Power Management

6.3.3 PCI Power Management Registers

Power Management registers are part of the capabilities linked list pointed to by the Capabilities

Pointer (Cap_Ptr) in the PCI configuration space. Refer to Section 4.1.

All fields are reset by LAN_PWR_GOOD. All of the fields except

PME_En and PME_Status are

reset by the deassertion (rising edge) of RST#. If AUX_POWER = 0b, the

PME_En and

PME_Status fields also reset by the deassertion (rising edge) of RST#.

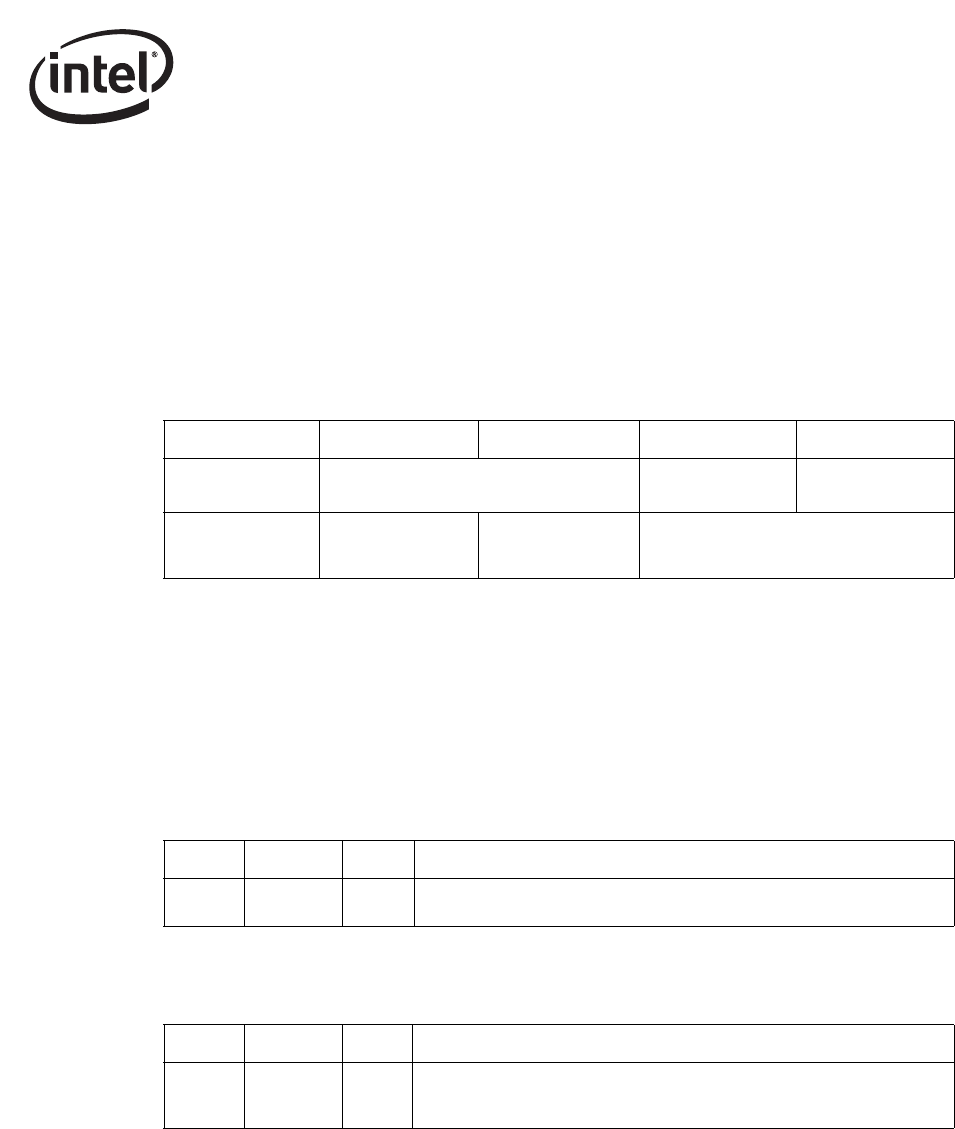

The following table lists the organization of the PCI Power Management Register Block:

The following sections describe the register definitions, whether they are required or optional for

compliance, and how they are implemented in the Ethernet controller. Complete details can be

found in the PCI Power Management Interface specification.

Note: The offset indicated is the byte-offset from the position indicated by Cap_Ptr in the Configuration

Space Header.

6.3.3.1 Capability ID

1 Byte Offset = 0 (RO)

6.3.3.2 Next Item Pointer

1 Byte Offset = 1 (RO)

Byte Offset Byte 3 Byte 2 Byte 1 Byte 0

DCh

Power Management Capabilities

(PMC)

Next Item Ptr Capability ID

E0h Data

PMCSR_BSE

Bridge Support

Extensions

Power Management Control / Status

Register (PMCSR)

Bits Default R/W Description

07:00 01h

Read

Only

ID – The Ethernet controller returns a value of 01h for this field, indicating

the linked list item as being the PCI Power Management Registers.

Bits Default R/W Description

07:00 E4h

Read

Only

Next Item Pointer - This field provides an offset into the function’s PCI

Configuration Space pointing to the location of next item in the function’s

capability list. Its value of E4h points to the PCI-X

a

capability.

a. Not applicable to the 82541xx, 82547GI/EI, or 82540EP/EM.