Software Developer’s Manual 227

Register Descriptions

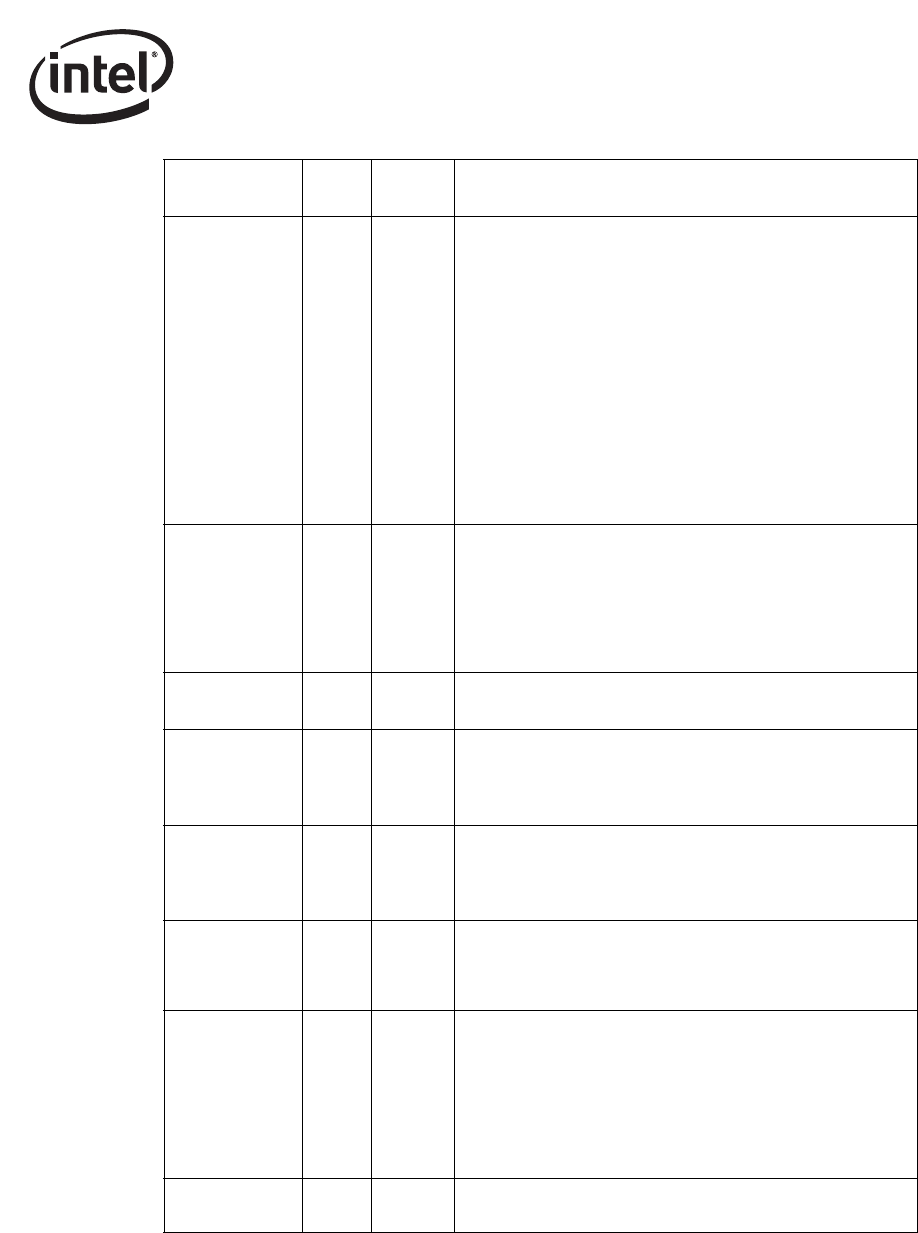

SPEED 7:6 X

Link speed setting

Indicates the configured speed of the link.

These bits are either forced by software when forcing the link

speed through the CTRL.SPEED control bits, automatically set

by hardware when Auto-Speed Detection is enabled or reflect

the internal indication inputs from the PHY.

When Auto-Speed Detection is enabled, the Ethernet

controller’s speed is configured only once after the internal link

is asserted.

Speed indication is mapped as follows:

00b = 10 Mb/s

01b = 100 Mb/s

10b = 1000 Mb/s

11b = 1000 Mb/s

These bits are not valid in TBI mode/internal SerDes.

ASDV 9:8 X

Auto Speed Detection Value

Indicates the speed sensed by the Ethernet controller from the

internal PHY. The ASDV status bits are provided for diagnostics

purposes. The ASD function can be initiated by software writing

a logic 1b to the CTRL_EXT.ASDCHK bit. The resultant speed

detection is reflected in these bits. See Section 13.4.6 for

details.

Reserved 10 X

Reserved

Reads as 0b.

PCI66 11 X

PCI Bus speed indication

When set, indicates that the PCI bus is running at 66 MHz.

Reflects the M66EN input pin.

Note: Not applicable to the 82547GI/EI.

BUS64

1

12 X

PCI Bus Width indication

When set, indicates that the Ethernet controller is sitting on a

64-bit PCI/PCI-X bus. BUS64 is determined by REQ64#

assertion.

PCIX_MODE

1

13 X PCI-X Mode indication

When set to 1b, the Ethernet controller is operating in PCI-X

Mode; otherwise, the Ethernet controller is operating in

conventional PCI Mode.

PCIXSPD

1

15:14 X PCI-X Bus Speed Indication

Attempts to indicate the speed of the bus when operating in a

PCI-X bus. Only valid when STATUS.PCIX_Mode = 1b.

00b = 50-66 MHz

01b = 66-100 MHz

10b = 100-133 MHz

11b = Reserved

Reserved 31:16 0b Reserved

Reads as 0b.

1. Not applicable to the 82540EP/EM, 82541xx, or 82547GI/EI.

Field Bit(s)

Initial

Value

Description