72

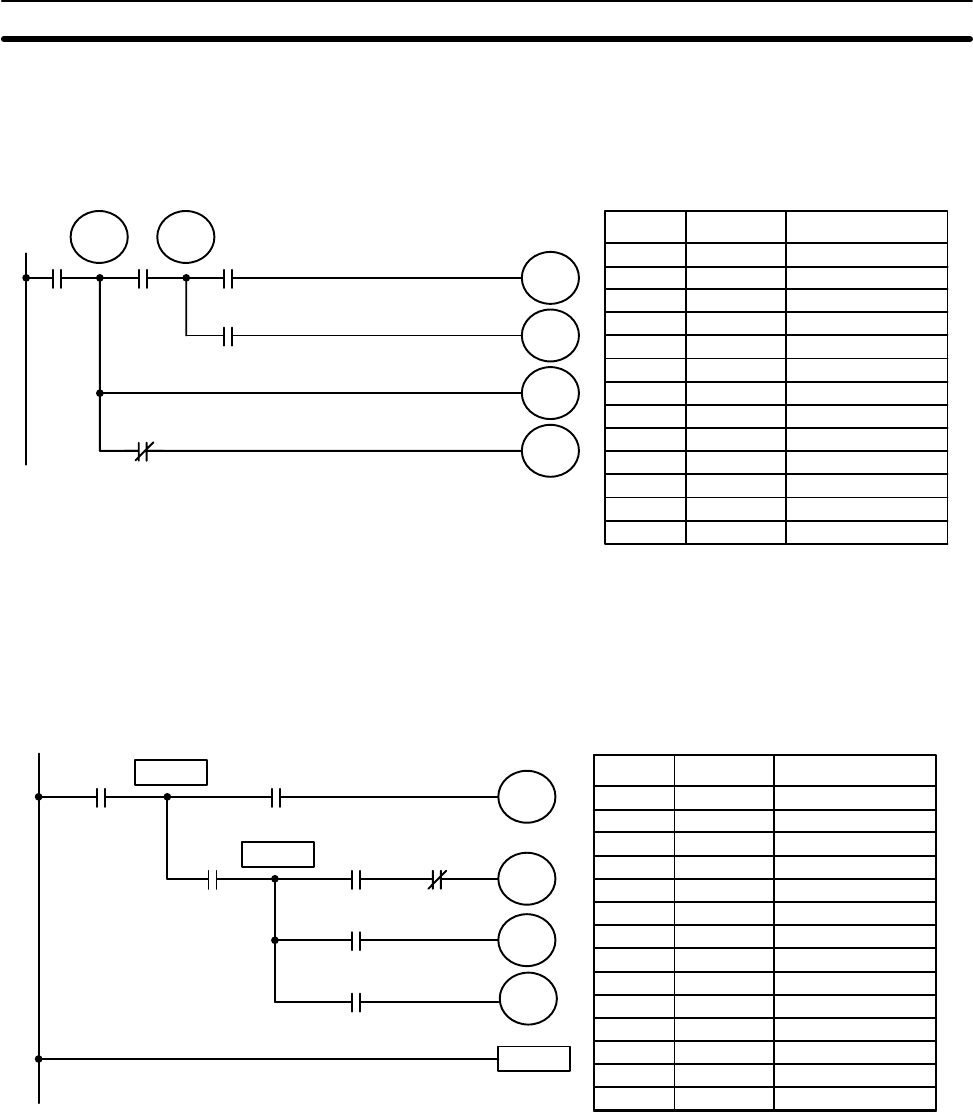

If the condition assigned 0004 was not in the diagram, the second LD using

TR 0 would not be necessary because OUT with 0102 and the AND NOT

with 0005 both require the same execution condition, i.e., the execution con-

dition stored in TR 0. The diagram and mnemonic code for this program are

shown below.

0000 0001 0002

0003

0005

0100

0101

0102

0103

TR

0

TR

1

Address Instruction Operands

0000 LD 0000

0001 OUT TR 0

0002 AND 0001

0003 OUT TR 1

0004 AND 0002

0005 OUT 0100

0006 LD TR 1

0007 AND 0003

0008 OUT 0101

0009 LD TR 0

0010 OUT 0102

0011 AND NOT 0005

0012 OUT 0103

When coding IL(02) and ILC(03), the mnemonic code will be the same re-

gardless of whether the instruction is drawn as branching instruction lines or

whether IL(02) is placed on its own instruction line. If drawn as branching

instruction lines, each branch line is coded as if it were connected to the bus

bar, i.e., the first condition on each branch line corresponds to a LD or LD

NOT instruction.

0002

0000

0001

ILC(03)

IL(02)

0004

IL(02)

0006

0005

0003

0100

0101

0102

0103

Address Instruction Operands

0000 LD 0000

0001 IL(02)

0002 LD 0001

0003 OUT 0100

0004 LD 0002

0005 IL(02)

0006 LD 0003

0007 AND NOT 0004

0008 OUT 0101

0009 LD 0005

0010 OUT 0102

0011 LD 0006

0012 OUT 0103

0013 ILC(03)

Interlocks

Data Areas, Definer Values, and Flags Section 5-4