30

4-3-3 Ladder Instructions

The ladder instructions are those that correspond to the conditions on the

ladder diagram. Ladder instructions, either independently or in combination

with the logic block instructions described next, form the execution conditions

upon which all other instructions are executed.

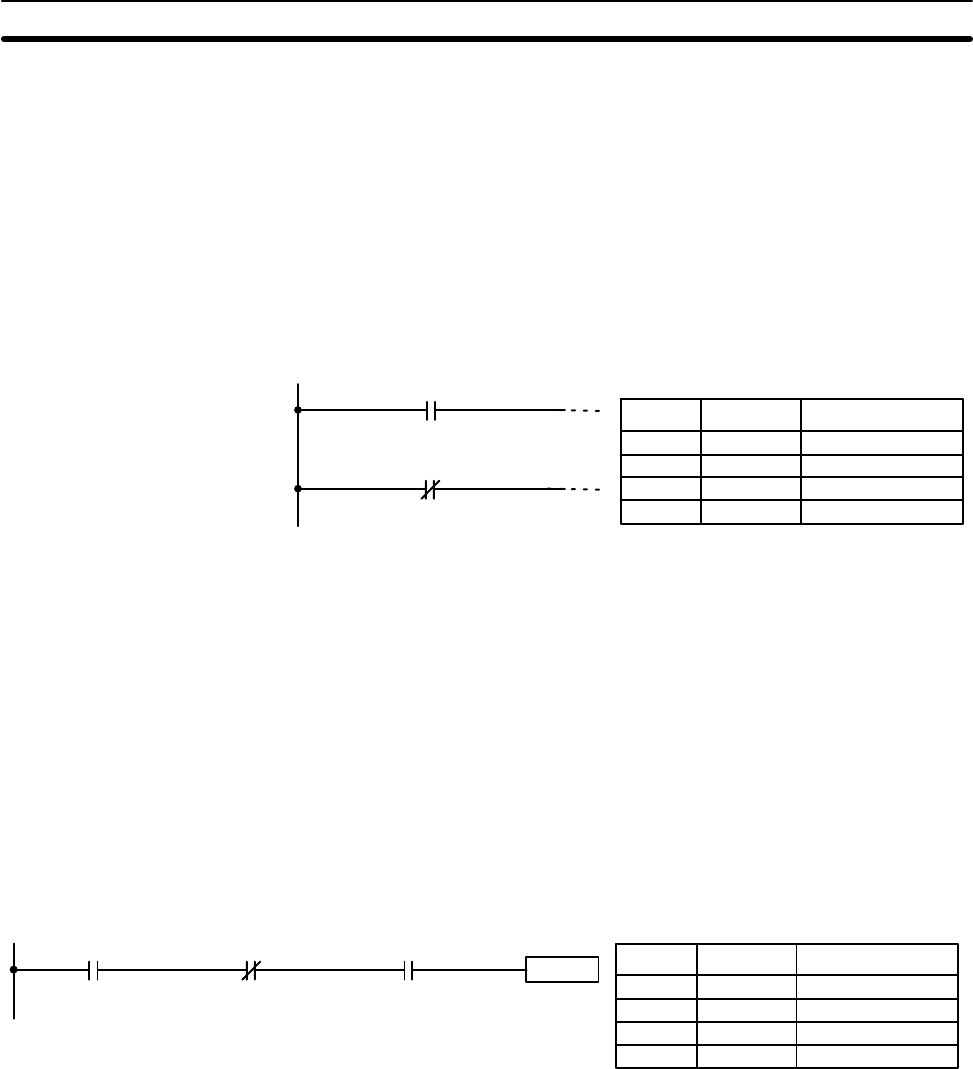

The first condition that starts any logic block within a ladder diagram corre-

sponds to a LOAD or LOAD NOT instruction.

0000

0000

A LOAD instruction.

A LOAD NOT instruction.

Address Instruction Operands

0000 LD 0000

0001 Instruction

0002 LD NOT 0000

0003 Instruction

When this is the only condition on the instruction line, the execution condition

for the instruction at the right is ON when the condition is ON. For the LOAD

instruction (i.e., a normally open condition), the execution condition would be

ON when IR 0000 was ON; for the LOAD NOT instruction (i.e., an normally

closed condition), it would be ON when IR 0000 was OFF.

When two or more conditions lie in series on the same instruction line, the

first one corresponds to a LOAD or LOAD NOT instruction; the rest of the

conditions, to AND or AND NOT instructions. The following example shows

three conditions which correspond in order from the left to a LOAD, an AND

NOT, and an AND instruction.

0000 0100 HR 000

Instruction

Address Instruction Operands

0000 LD 0000

0001 AND NOT 0100

0002 AND HR 000

0003 Instruction

The instruction at the right would have an ON execution condition only when

all three conditions are ON, i.e., when IR 0000 was ON, IR 0100 was OFF,

and HR 000 was ON.

Actually, AND instructions can be considered individually in series, each of

which would take the logical AND between the execution condition (i.e., the

sum of all conditions up to that point) and the status of the AND instruction’s

operand bit. If both of these were ON, an ON execution condition would be

produced for the next instruction. The execution condition for the first AND

instruction in a series would be the first condition on the instruction line.

Each AND NOT instruction in a series would take the logical AND between

its execution condition and the inverse of its operand bit.

LOAD and LOAD NOT

AND and AND NOT

The Ladder Diagram Section 4-3