99

Note that in the program just mentioned, the present value in the counter

buffer is transferred to counter number 47 at points A and B. In this case, if

S31 (=1,000) < S < S32 (=2,000) and S33 (=2,000) < S < S34 (=3,000), and

if the present count value of the first high-speed counter (at point A) is 1,999

and that of the second counter (at point B) is 2,003, HR 015 and HR100 may

be simultaneously turned ON. If it is necessary to avoid this, set the values of

S32 and S33 so that there is a value difference equivalent to the time lag

from points A to B. For example, set the value of S32 to 2,000 and that of

S33 to 2,010.

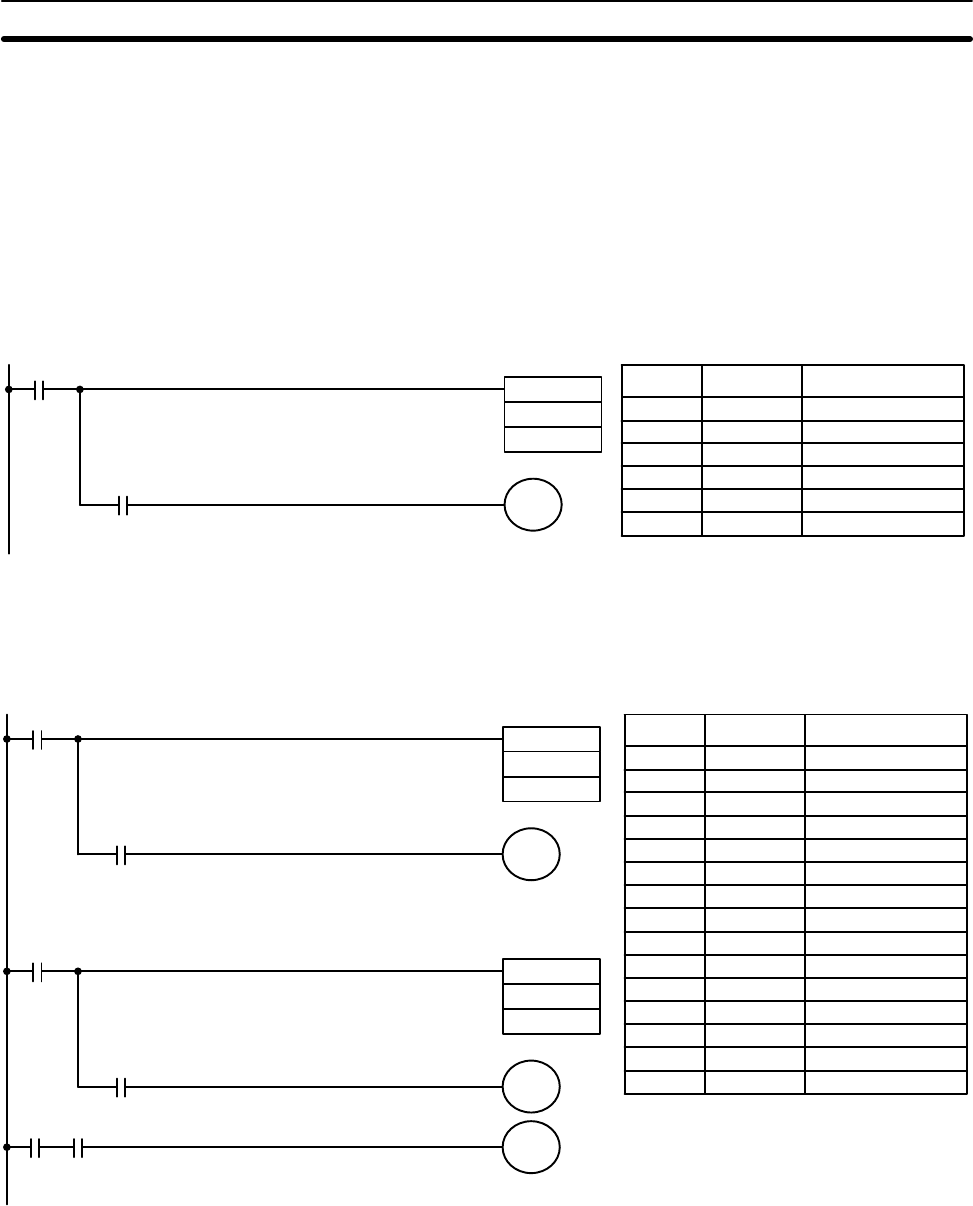

More than 16 output bits may be obtained using CMP.

1813 (normally ON)

1905 (GR)

0600

CMP(20)

CNT 47

#6850

Address Instruction Operands

0000 LD 1813

0001 CMP(20)

CNT 47

# 6850

0002 AND 1905

0003 OUT 0600

In the above program, output 0600 is turned ON when the following condition

is satisfied, where S is the present count value of the high-speed counter:

6,850 < S ≤ 9,999.

1813 (normally ON)

1905 (GR)

1000

CMP(20)

CNT 47

#0300

1813 (normally ON)

1907 (LE)

1001

CMP(20)

CNT 47

#2300

1000 1001

0601

Address Instruction Operands

0000 LD 1813

0001 CMP(20)

CNT 47

# 0300

0002 AND 1905

0003 OUT 1000

0004 LD 1813

0005 CMP(20)

CNT 47

# 2300

0006 AND 1907

0007 OUT 1001

0008 LD 1000

0009 AND 1001

0010 OUT 0601

In the above program, output 0601 is turned ON when the following condition

is satisfied, where S is the present count value of the high-speed counter:

300 < S < 2,300.

The number of digits of the upper and lower limits of the high-speed counter

can be increased from four to eight by using the high-speed counter together

with CNTR and CMP.

Cascade Connection

(Counting Past 9,999)

Timer and Counter Instructions Section 5-11