Standard Commands for Programmable Instruments (SCPI)

100

Query Syntax STATus:OPERtion:EVENt?

Returned Parameters <NR1> (Register Value)

Examples STAT: OPER: EVEN? STATUS: OPERATIONAL: EVENT?

NTR/PTR Commands

These commands allow you to set or read the value of the Operation NTR (Negative-

Transition) and PTR (Positive-Transistion) registers. These registers serve as polarity filters

between the Operation Enable and Operation Event registers to cause the following actions:

♦

When a bit of the Operation NTR register is set to 1 then a 1-to-0 transition of a corresponding enabled bit of Operation

Condition register will cause that bit to be set in the Operation Event register.

♦

When a bit of the Operation PTR register is set to 1 then a 0-to-1 transition of a corresponding enabled bit of Operation

Condition register will cause that bit to be set in the Operation Event register.

♦

If the same bits in both NTR and PTR registers are set to 1, then

any transition of that bit (if enabled) at the Operation

Condition register will set the corresponding bit in the Operation Event register.

♦

If the same bits in both NTR and PTR registers are set to 0, then

no transition of that bit (even if enabled) at the

Operation Condition register can set the corresponding bit in the Operation Event register.

NOTE If a Operation bit is in the proper state, then programming the corresponding1 PTR or NTR filter bit to 1

will set the associated Event Register bit.

Command Syntax STATus:OPERtion:NTRansition <NRf>

STAT

us:OPERtion:PTRansition <NRf>

Parameters 0 to 32727

Default Value 0

Examples STAT:OPER:NTR32 STATUS:OPERATION:PTR 1312

Query Syntax STAT:OPER:NTR? STAT:OPER:PTR?

Returned Parameters <NR1>

(Register value)

STAT:PRES

This command sets all defined bits in the Status Subsystem PTR registers and clears all bits in the subsytem NTR and

Enable registers. STAT:OPER:PTR is set to 1313 and STAT:QUES:PTR is set to 1555.

Command Syntax STATus:PRESet

Examples STAT: PRES STATUS: PRESET

Status Questionable Registers

The bit configuration of all Status Questionable registers is as follows:

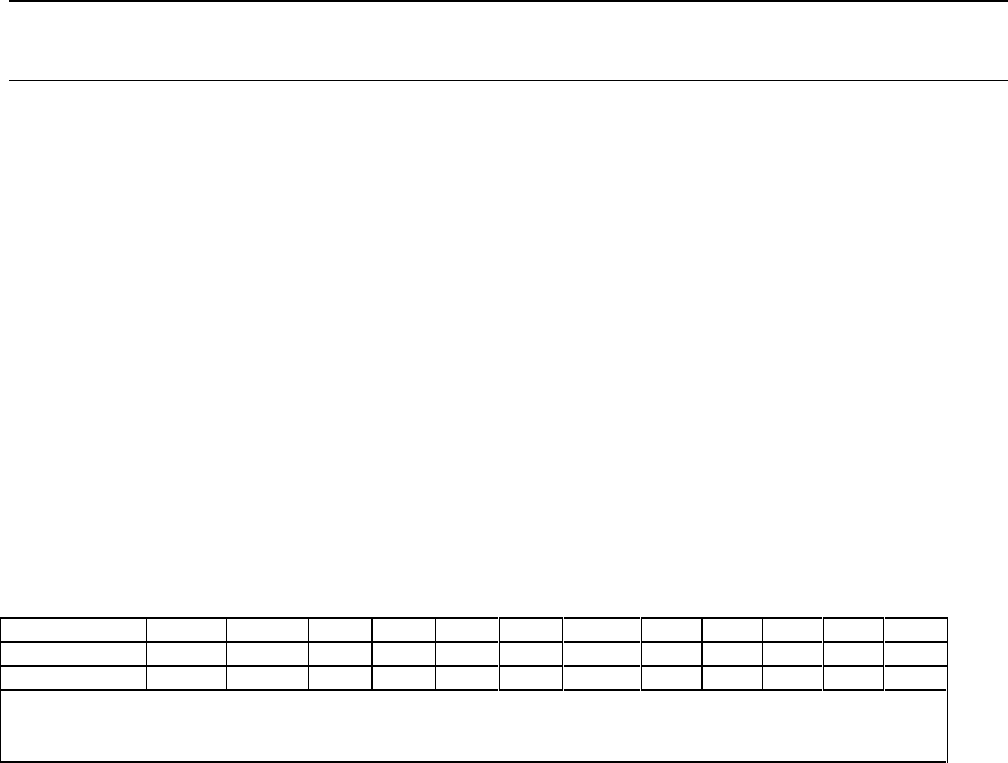

Bit Configuration of Questionable Registers

Bit Position 15-1110 9876 5 43210

Condition NU UNR RI NU NU NU NU TO NU NU OC OV

Bit Weight 1024 512 256 128 64 32 16 8 4 2 1

NU = (Not used); OC = Overcurrent protection circuit has tripped; OT = Overtemperature status condition exists;

OV = Overvoltage protection circuit has tripped; RI = Remote inhibit is active; UNR = Power supply output is

unregulated.

See "Status Reporting" for more explanation of these registers.